128 www.xilinx.com Embedded Tri-Mode Ethernet MAC User Guide

UG074 (v2.2) February 22, 2010

Chapter 4: Physical Interface

R

If the PHY device sources the receiver SGMII stream synchronously from the shared

oscillator (refer to the PHY data sheet), the MGT receives data at exactly the same rate

as that used by the core. That is, the RX elastic buffer neither empties nor fills because

the same frequency clock is on either side.

In this situation, the RX elastic buffer does not underflow or overflow, and the RX

elastic buffer implementation in the MGT is recommended to save logic resources.

• Case 2

Using the case illustrated by Figure 4-17, assume that both clock sources used are

50 ppm. The maximum frequency difference between the two devices is 100 ppm,

translating into a full clock period difference every 10000 clock periods and resulting

in a requirement for 16 FIFO entries above and below the half-full point. This case

provides reliable operation with the MGT RX elastic buffers. However, the designer

must check the PHY data sheet to ensure that the PHY device sources the receiver

SGMII stream synchronously to its reference oscillator.

Using the FPGA Logic Elastic Buffer

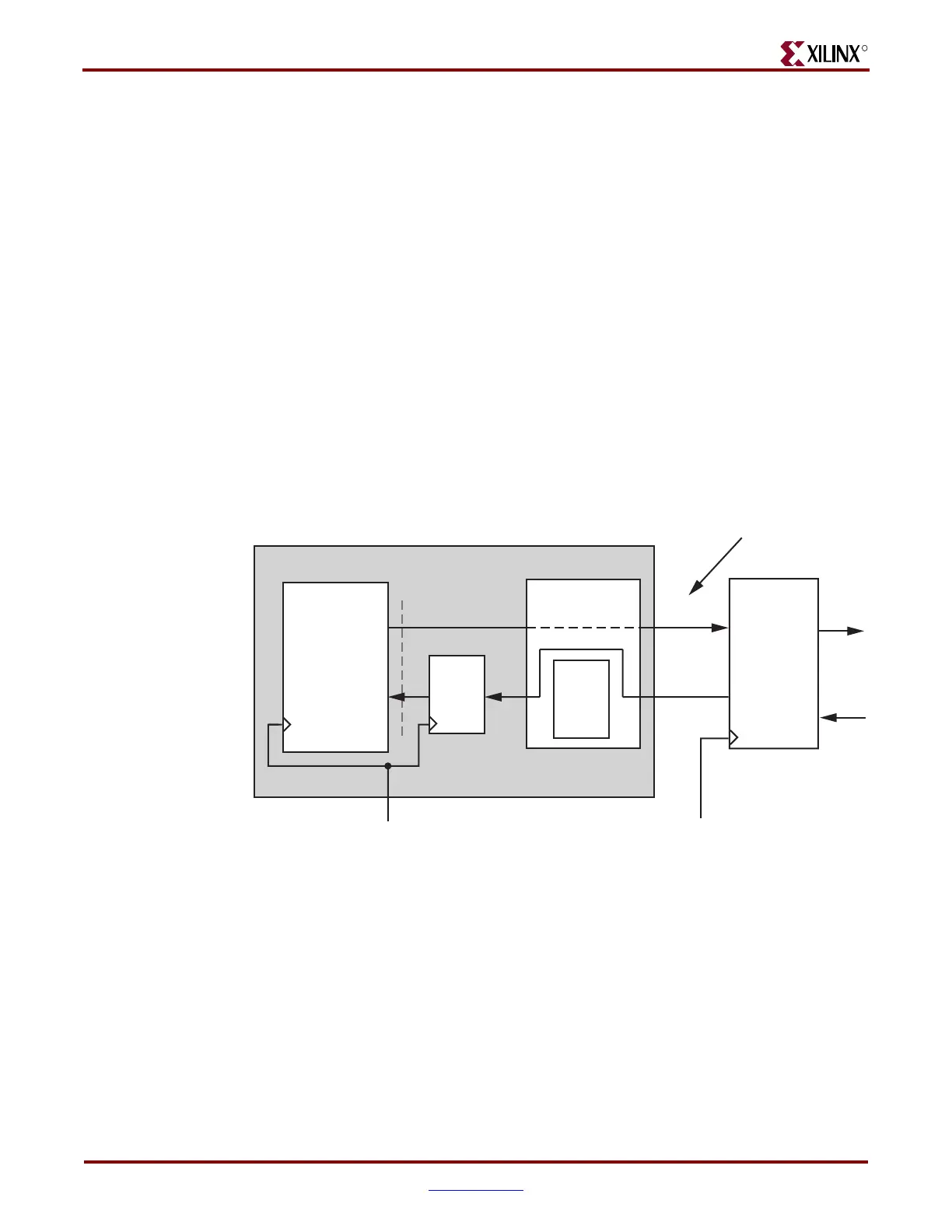

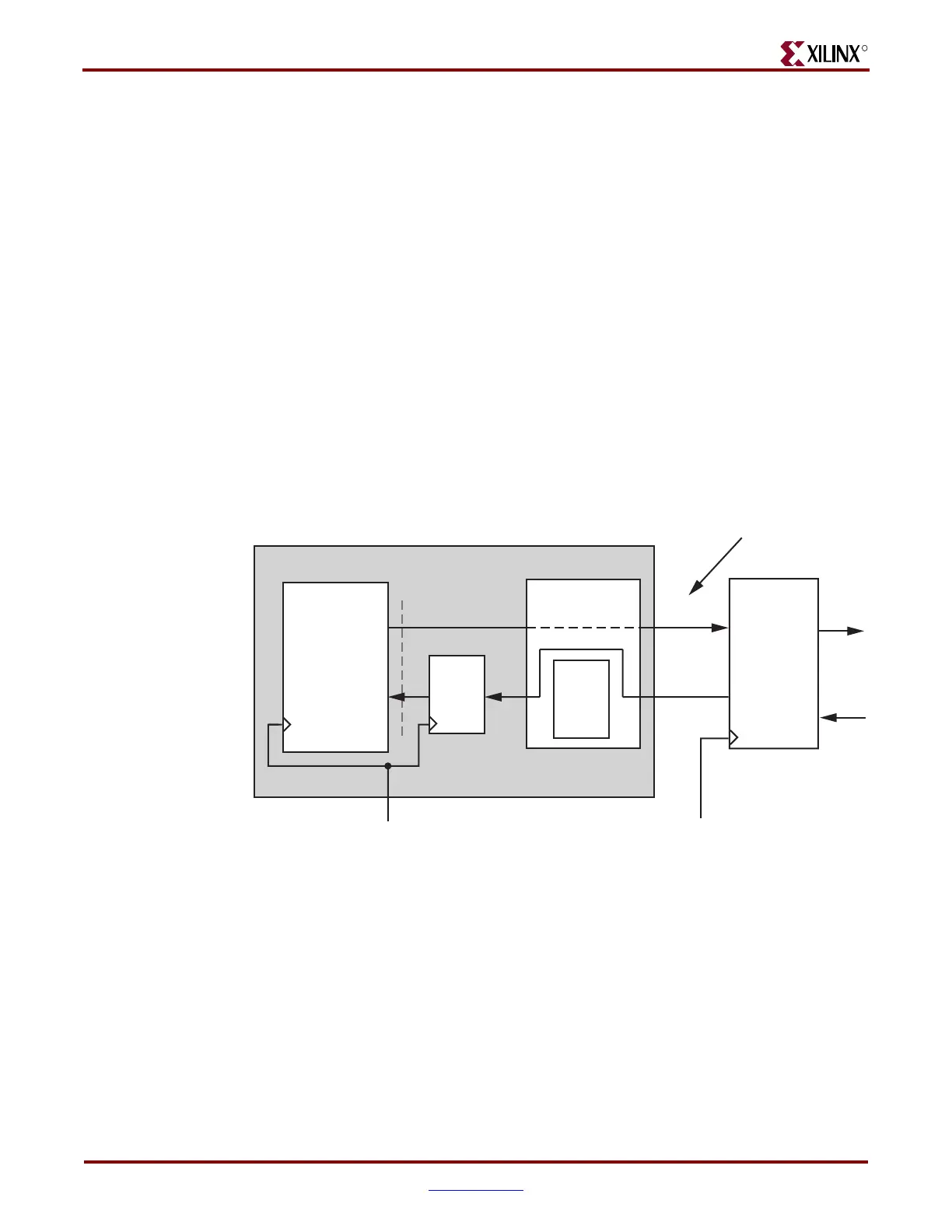

Figure 4-21 illustrates a simplified diagram of a situation where the Ethernet MAC in

SGMII mode is interfaced to an external PHY device with an independent clock. The

MGT’s elastic buffer has been bypassed and the FPGA elastic buffer is used.

Using the SGMII in this configuration eliminates the possibility of buffer error if the clocks

are not tightly controlled enough to use the MGT elastic buffer.

Figure 4-21: SGMII Implementation Using a Logic Buffer

Ethernet MAC MGT

TXP/TXN

RXP/RXN

Tw isted

Copper

Pair

SGMII Link

10BASE-T

100BASE-T

1000BASE-T

PHY

FPGA

125MHz + 100 ppm125 MHz – 100 ppm

GT11

Elastic

Buffer

RX

Elastic

Buffer

UG074_3_83_012408

Loading...

Loading...