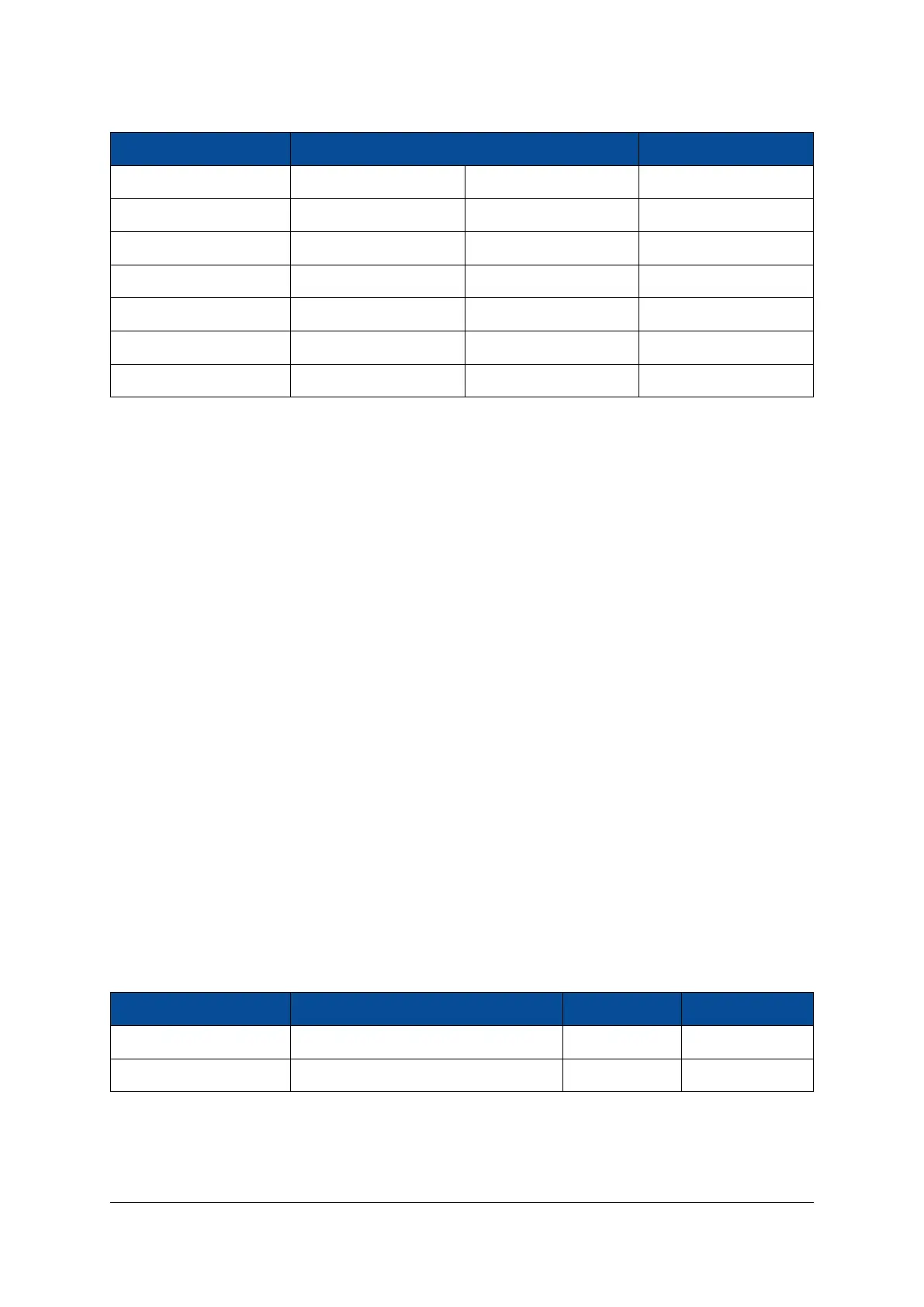

Nand Cycle Parameter CS0 CS0 Cycles Description

T_RC 30 4 Read cycle time

T_WC 30 4 Write cycle time

T_REA 0 1 RE assertion delay

T_WP 20 3 WE deassertion delay

T_CLR 20 3 Page cycle time

T_AR 20 3 ID read time

T_RR 30 4 Busy to RE

Table 24: NAND Flash Parameters

2.17 SD Card

An SD card can be connected to the PS MIO pins 40-45 or 46-51, or alternatively via EMIO pins to the PL.

The corresponding MIO pins are available on the module connector. Note that only MIO pins 40-45 allow

the Mars ZX3 SoC module to boot from the SD card. Information on this boot mode is available in Section

3.6.

Please note that external pull-ups are needed for SD card operation. Depending on the selected voltage

for VCC_CFG_PS_B13_B33, a level shifter to 3.3 V may be required (some level shifters also have built-in

pull-ups).

2.18 Gigabit Ethernet

A 10/100/1000 Mbit Ethernet PHY is available on the Mars ZX3 SoC module, connected to the PS and PL via

RGMII interface.

Please note that Xilinx recommends operation at 1.8 V/2.5 V for the RGMII interface for the MIO pins [18].

Enclustra tests have shown that the RGMII is functional with a 3.3 V I/O voltage on the MIO pins, as long

as the I/O voltage configured in Vivado matches the applied I/O voltage. However, in situations where a

voltage of 3.3 V for VCC_CFG_PS_B13_B33 is required, it is recommended to assign the Ethernet PHY signals

to FPGA logic and use the GMII to RGMII converter provided by Xilinx [21], instead of using 3.3 V on the

MIO pins.

2.18.1 Ethernet PHY Type

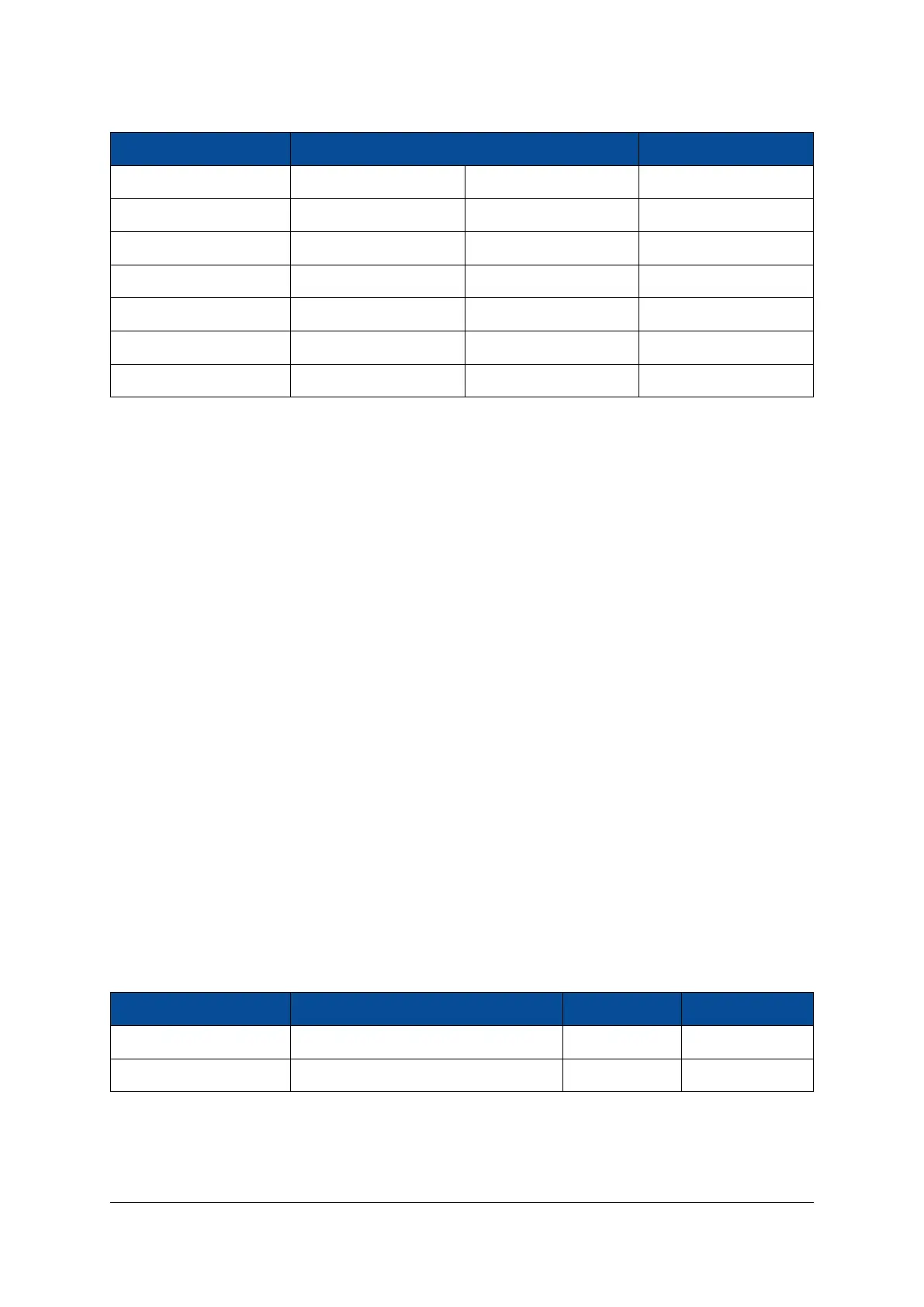

Table 25 describes the equipped Ethernet PHY device type on the Mars ZX3 SoC module.

Module PHY Type Manufacturer Type

MA-ZX3 - R1 KSZ9021RN Micrel 10/100/1000 Mbit

MA-ZX3 - R2 and newer KSZ9031RNX Micrel 10/100/1000 Mbit

Table 25: Gigabit Ethernet PHY Type

D-0000-424-004 29 / 48 Version 05, 21.08.2018

Loading...

Loading...