Five 16-bit memory chips are used to build an 72-bit wide memory (8 bits are unused): 64 bits for data and

8 bits for ECC.

Please note that on the smallest module configuration (ME-XU6-2CG-1E-D10H) the DDR4 chip for ECC and

half of the DDR4 chips for data are not equipped; in total 2 memory chips are used for the PS DDR4 SDRAM.

Similarly, on configurations without ECC, the fifth DDR4 chip is missing.

The maximum memory bandwidth on the Mercury+ XU6 SoC module regular variants (full bandwidth) is:

2400 Mbit/sec × 64 bit = 19200 MB/sec

and for the smallest variant (half bandwidth) is:

2400 Mbit/sec × 32 bit = 9600 MB/sec

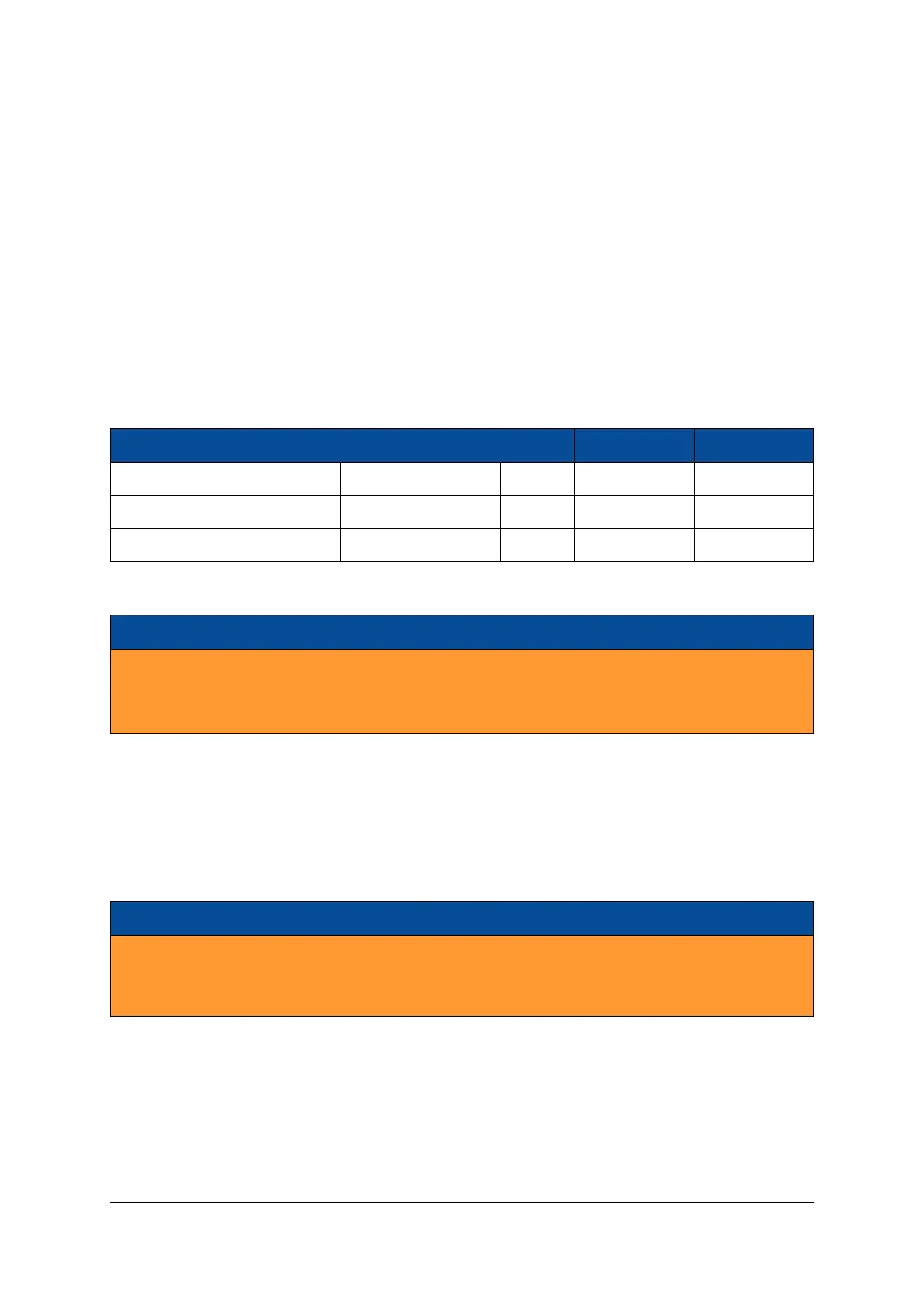

2.15.1 DDR4 SDRAM Type

Table 23 describes the memory availability and configuration on the Mercury+ XU6 SoC module.

Module SDRAM Type Density Configuration Manufacturer

ME-XU6-D10H/D11 K4A4G165WE-BIRC 4 Gbit 256 M × 16 bit Samsung

ME-XU6-D12/D12E K4A8G165WB-BIRC 8 Gbit 512 M × 16 bit Samsung

ME-XU6-D13E H5ANAG6NCMR-XNI 16 Gbit 1 G × 16 bit SK Hynix

Table 23: DDR4 SDRAM (PS) Types

Warning!

Other DDR4 memory devices may be equipped in future revisions of the Mercury+ XU6 SoC module.

Please check the user manual regularly for updates. Any parts with different speed bins or temperature

ranges that fulfill the requirements for the module variant may be used.

2.15.2 Signal Description

Please refer to the Mercury+ XU6 SoC Module FPGA Pinout Excel Sheet [4] for detailed information on the

DDR4 SDRAM connections.

2.15.3 Termination

Warning!

No external termination is implemented for the data signals on the Mercury+ XU6 SoC module. There-

fore, it is strongly recommended to enable the on-die termination (ODT) feature of the DDR4 SDRAM

device.

2.15.4 Parameters

Please refer to the Mercury+ XU6 SoC module reference design [2] for DDR4 settings guidelines.

The DDR4 SDRAM parameters to be set in the Vivado project are presented in Table 24.

D-0000-464-001 35 / 58 Version 02, 21.07.2021

Loading...

Loading...