Chapter 8 Built-in High-speed Counter Function

8-1

Chapter 8 Built-in High-speed Counter Function

XGB series have built-in function of High-speed counter in main unit. This chapter describes specifications and

usage of High-speed counter’s function.

8.1 High-speed Counter Specifications

It describes specifications, setting and usage of function, programming and wiring with external device of

built-in main unit.

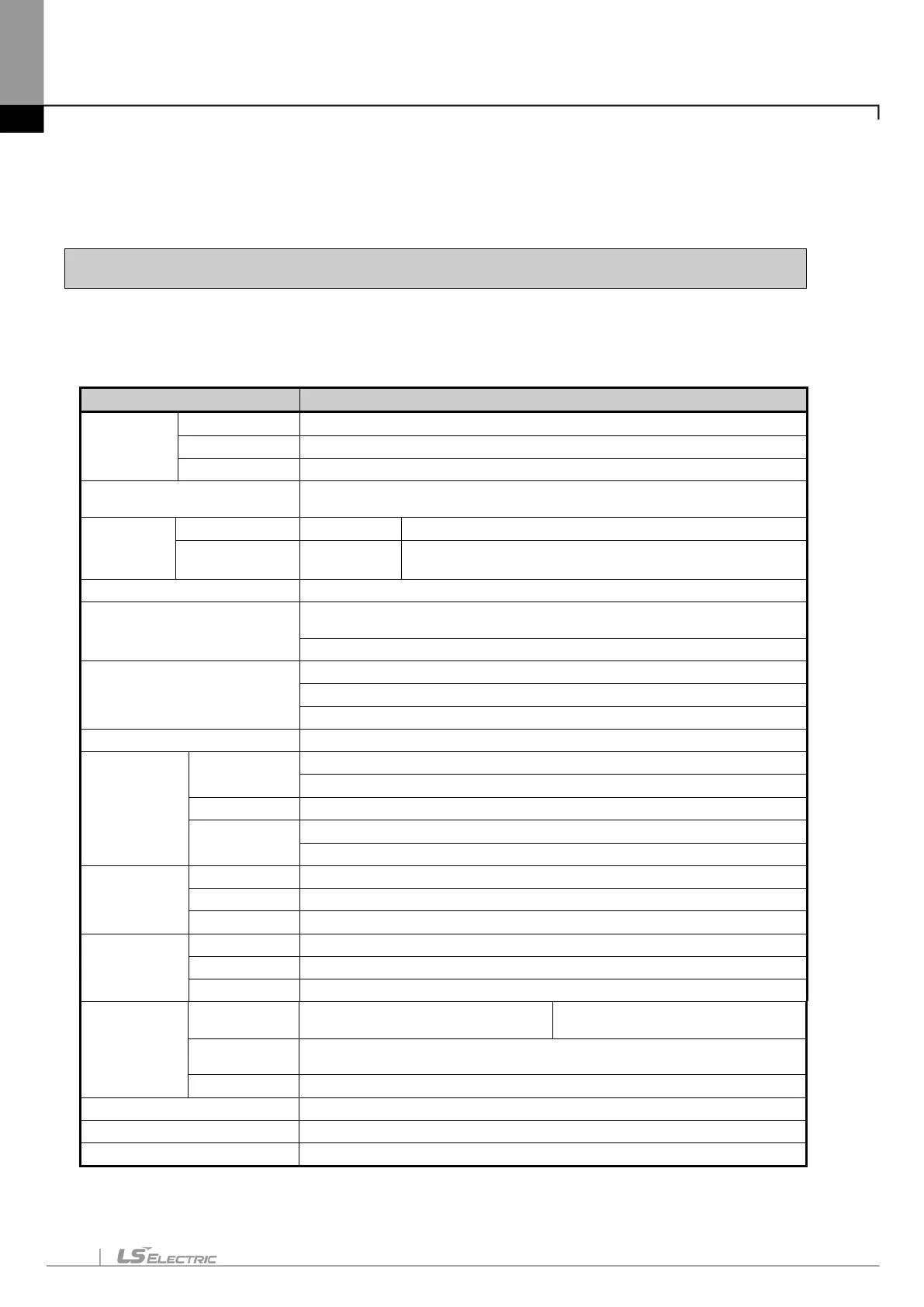

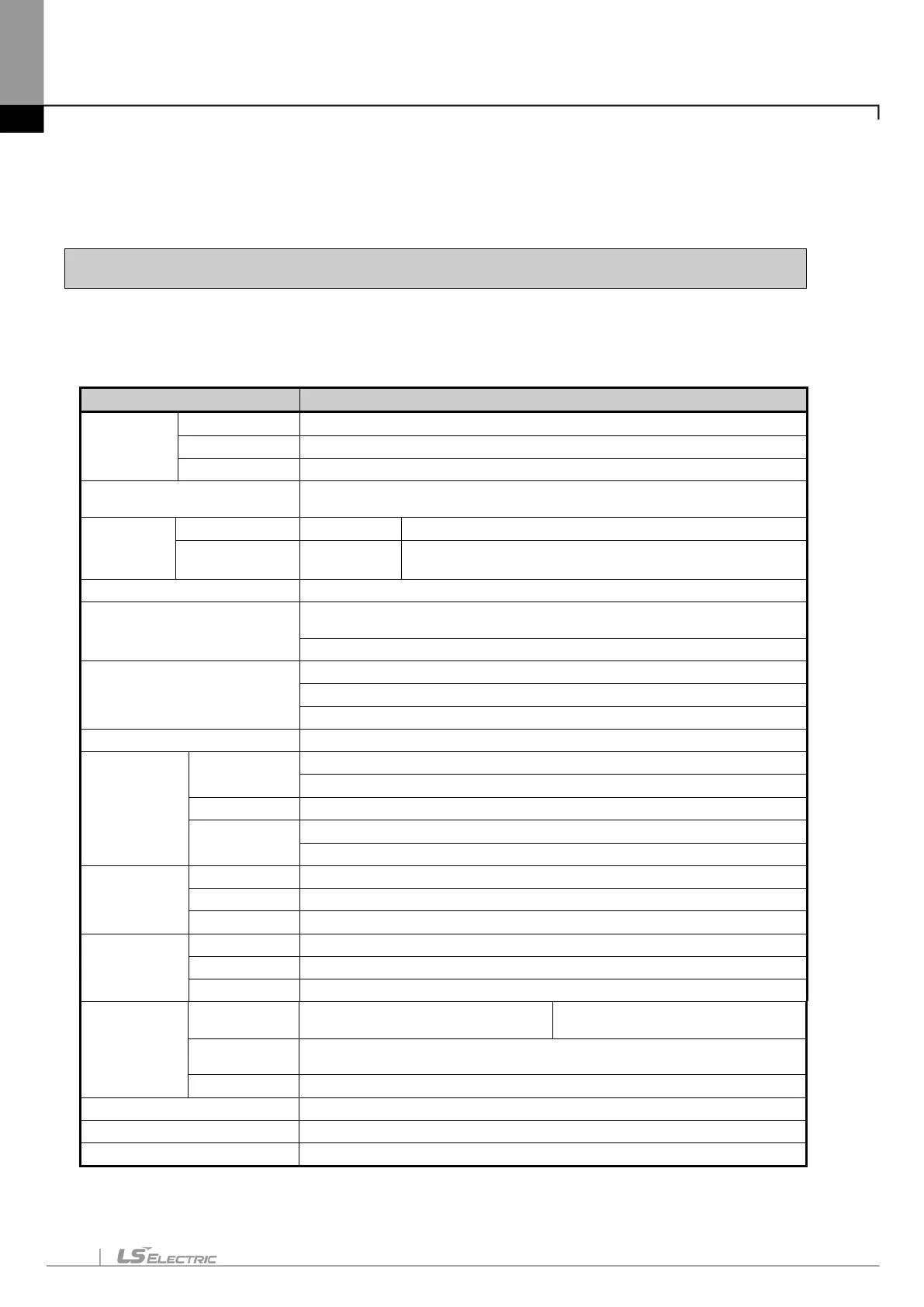

8.1.1 Performance specifications

(1) Performance specification

Count input

signal

Voltage input (Open collector)

Max. coefficient speed

Number of

channels

100kpps (ch0,1,2,3) / 20kpps (ch4,5,6,7)

※1

2 phase 4 channels

50kpps (ch0,2) / 10kpps (ch4,6)

※1

But, In case of 4 multiplication: 50kpps (ch0,2) / 8kpps (ch4,6)

Signed 32 Bit (-2,147,483,648 ~ 2,147,483,647)

Count mode

(Program setting)

Linear count (if 32-bit range exceeded, Carry/Borrow occurs)

Counter max. and min. value is indicated

Ring count (repeated count within setting range)

Input mode

(Program setting)

Up/Down

setting

1 phase input

Increasing/decreasing operation setting by B-phase input

Increasing/decreasing operation setting by program

Automatic setting by difference in phase

CW/CCW

A-phase input: increasing operation

B-phase input: decreasing operation

Multiplication

function

Control input

External output

Output points

1 point/channel (for each channel)

:output contact point of main unit available

2 point/channel (for each channel)

:output contact point of main unit available

Type

Select single-compared (>, >=, =, =<, <) or section compared output (included or

excluded) (program setting)

Relay, Open-collector output (Sink)

To be set through program (count available only in enable status)

To be set through terminal (contact) or program

Auxiliary mode (program setting)

Latch counter, Count per unit time (time setting value: 1~60,000ms)

※1 : XEC-DR32(64)H/D1 unit supports 1-phase 10kpps, 2-phase 5kpps.

Loading...

Loading...