144 Appendix B: Technical information

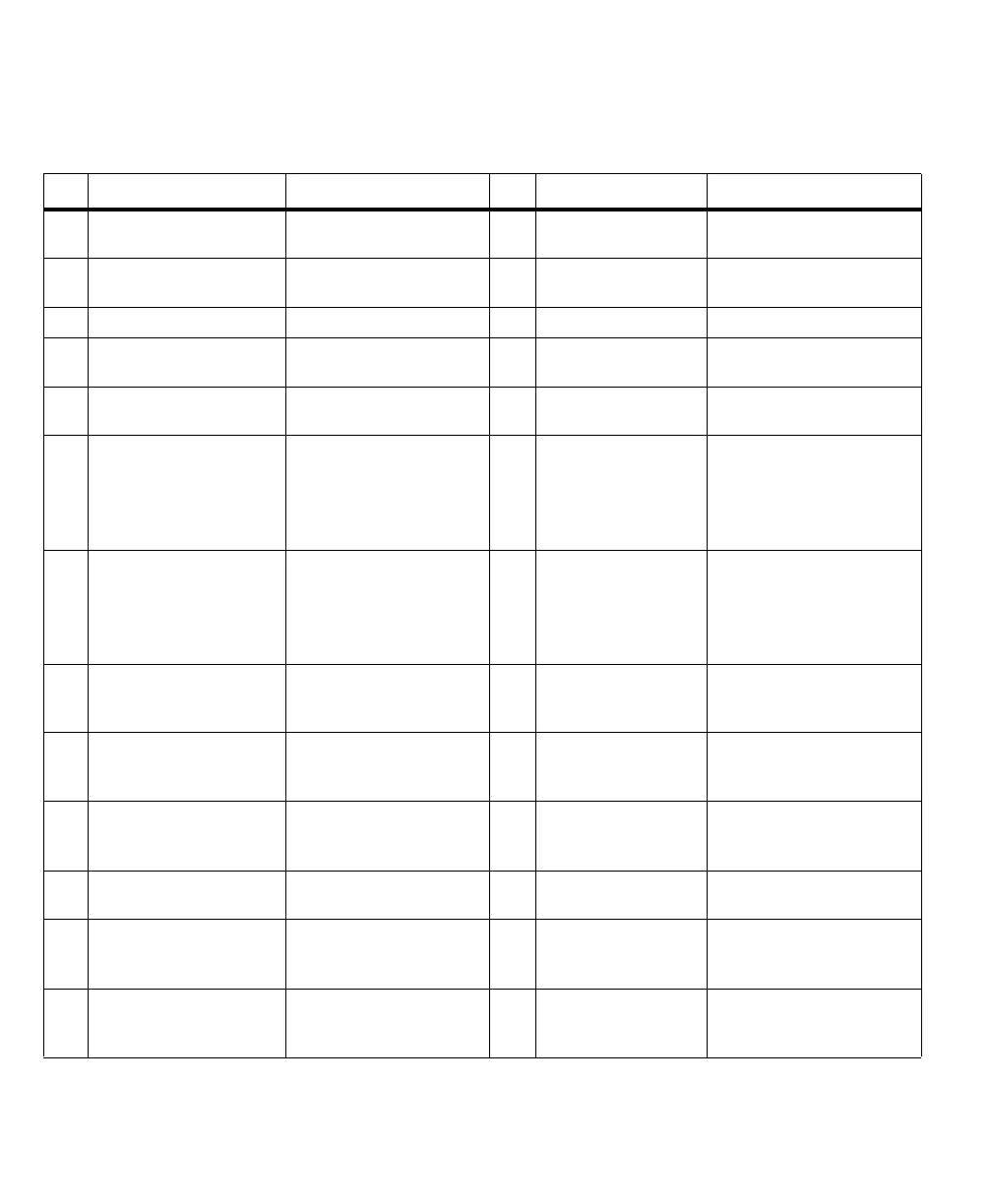

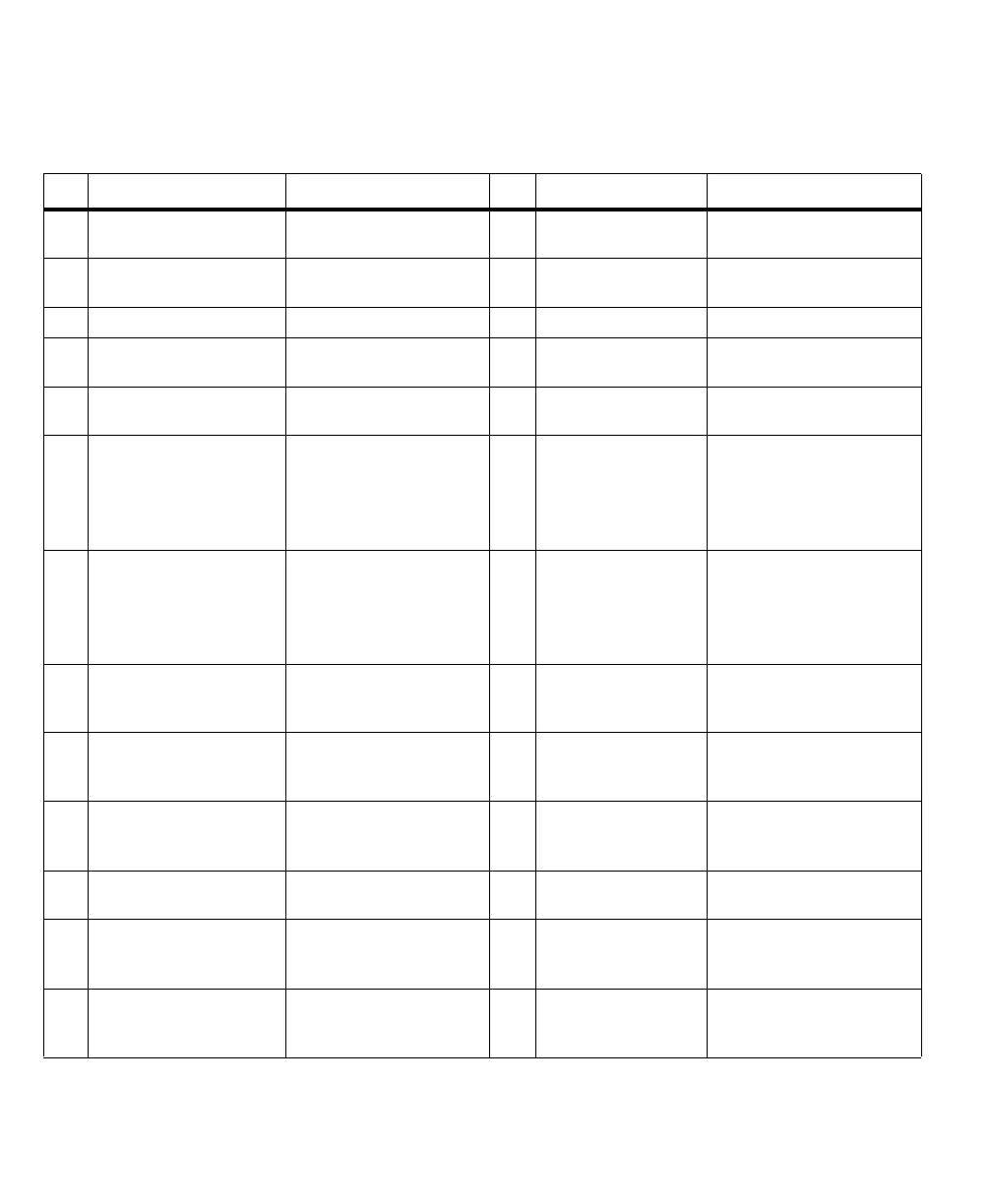

The pinout for DVI connector 1 is as follows:

Pin Signal

1

Description Pin Signal

1

Description

1 P3_LVDS/TTL_VSYNC_IO- VSYNC input/output for acq.

path 3 (negative).

17 P3_LVDS/TTL_CLK_IO- Clock input/output for acq.

path 3 (negative).

2 P3_LVDS/TTL_VSYNC_IO+ VSYNC input/output for acq.

path 3 (positive).

18 P3_LVDS/TTL_CLK_IO+ Clock input/output for acq.

path 3 (positive).

3 GND Ground. 19 GND Ground.

4 P2_LVDS/TTL_VSYNC_IO- VSYNC input/output for acq.

path 2 (negative).

20 P2_LVDS/TTL_CLK_IO- Clock input/output for acq.

path 2 (negative).

5 P2_LVDS/TTL_VSYNC_IO+ VSYNC input/output for acq.

path 2 (positive).

21 P2_LVDS/TTL_CLK_IO+ Clock input/output for acq.

path 2 (positive).

6 P3_TTL_AUX(EXP)_OUT TTL auxiliary output for acq.

path 3.

Supported signals: exposure

output 0 (main purpose) or

user-defined output 2.

22 P3_TTL_AUX(TRIG)_IN TTL auxiliary input for acq.

path 3.

Supported signals: trigger input

0 (main purpose), field input, or

user-defined input 0.

7 P3_RS232_RxD RS-232 serial input to acq.

path 3 of frame grabber

(UART).

23 P2_TTL_AUX(EXP)_OUT TTL auxiliary output for acq.

path 2.

Supported signals: exposure

output 0 (main purpose) or

user-defined output 2.

8 P3_RS232_TxD RS-232 serial output from

acq. path 3 (UART) to video

source.

24 P2_RS232_RxD RS-232 serial input to acq. path

2 of frame grabber (UART).

9 P3_LVDS/TTL_CHSYNC_IO- CSYNC input or HSYNC

input/output for acq. path 3

(negative).

C1 P0_VID_IN_B Video input B for acq. path 0

(AC/DC).

10 P3_LVDS/TTL_CHSYNC_IO+ CSYNC input or HSYNC

input/output for acq. path 3

(positive).

C2 P1_VID_IN_B Video input B for acq. path 1

(AC/DC).

11 GND Ground. C3 P2_VID_IN_B Video input B for acq. path 2

(AC/DC).

12 P2_LVDS/TTL_CHSYNC_IO- CSYNC input or HSYNC

input/output for acq. path 2

(negative).

C4 P3_VID_IN_B Video input B for acq. path 3

(AC/DC).

13 P2_LVDS/TTL_CHSYNC_IO+ CSYNC input or HSYNC

input/output for acq. path 2

(positive).

C5 GND Ground.

Loading...

Loading...