Matrox Solios eA/XA acquisition section 79

Note that only signals defined for acquisition path 0 (those beginning with P0)

and the common LVDS/TTL auxiliary signals apply to the Matrox Solios eA/XA

Single board. Only signals defined for acquisition paths 0 and 1 and the common

LVDS/TTL signals apply to the Matrox Solios eA/XA Dual board.

You can set TTL/LVDS signals in pairs to either TTL or LVDS format when

accessed from the external auxiliary I/O connector 0 (DB-44) of the cable adapter

board. For example, setting LVDS/TTL_AUX_IN2 to TTL also sets

LVDS/TTL_AUX_IN3 to TTL, and setting P0_LVDS/TTL_AUX_OUT0 to

LVDS also sets P0_LVDS/TTL_AUX_OUT1 to LVDS.

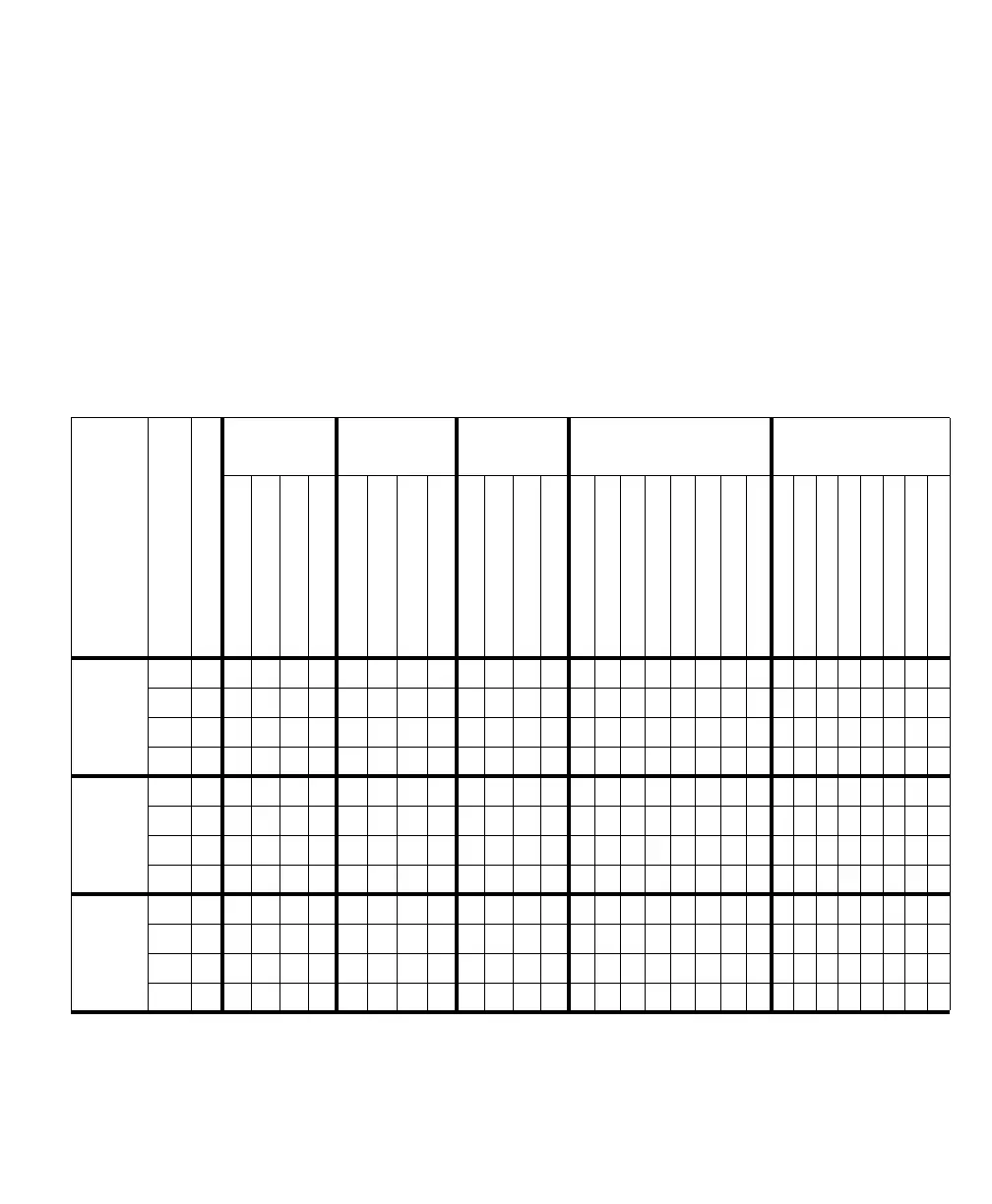

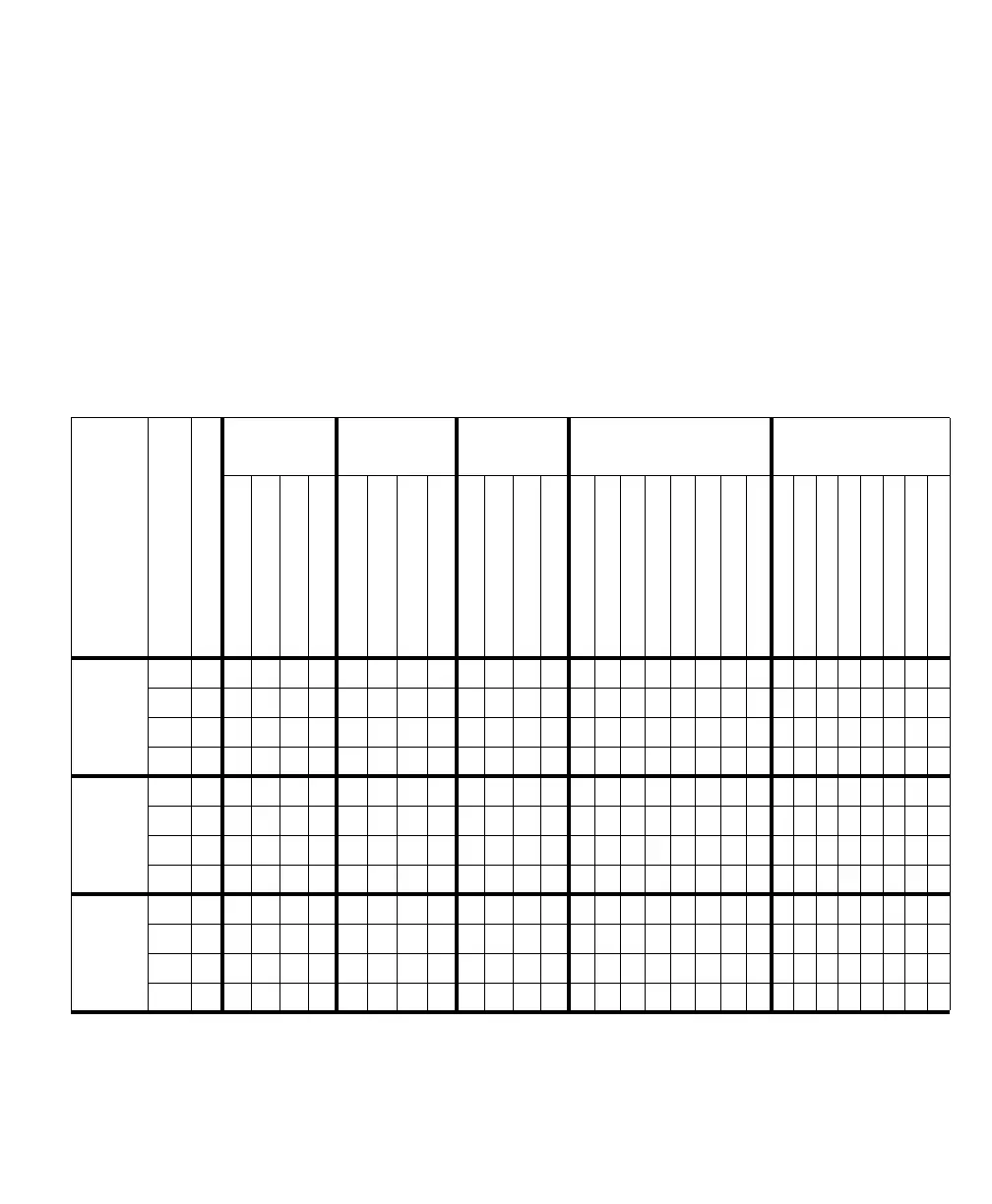

Type of

signal

Path#

Max # signals

1

TTL aux. input

2

TTL aux. output

2

Opto aux.

input

3

TTL/LVDS aux. input

4

TTL/LVDS aux. output

4

P0_TTL_AUX(TRIG)_IN

P1_TTL_AUX(TRIG)_IN

P2_TTL_AUX(TRIG)_IN

P3_TTL_AUX(TRIG)_IN

P0_TTL_AUX(EXP)_OUT

P1_TTL_AUX(EXP)_OUT

P2_TTL_AUX(EXP)_OUT

P3_TTL_AUX(EXP)_OUT

P0_OPTO_AUX(TRIG)_IN

P1_OPTO_AUX(TRIG)_IN

P2_OPTO_AUX(TRIG)_IN

P3_OPTO_AUX(TRIG)_IN

LVDS/T TL_AUX_ IN 0

LVDS/T TL_AUX_ IN 1

LVDS/T TL_AUX_ IN 2

LVDS/T TL_AUX_ IN 3

LVDS/T TL_AUX_ IN 4

LVDS/T TL_AUX_ IN 5

LVDS/T TL_AUX_ IN 6

LVDS/T TL_AUX_ IN 7

P0_LVDS/TTL_AUX_OUT0

P0_LVDS/TTL_AUX_OUT1

P1_LVDS/TTL_AUX_OUT0

P1_LVDS/TTL_AUX_OUT1

P2_LVDS/TTL_AUX_OUT0

P2_LVDS/TTL_AUX_OUT1

P3_LVDS/TTL_AUX_OUT0

P3_LVDS/TTL_AUX_OUT1

exposure

output

02 0 01

12 0 01

22 0 01

32 0 01

Trigger

input

0 4 0 1 23232323

1 4 0 1 23232323

2 4 0 1 23232323

3 4 0 1 23232323

Field

polarity

input

010 0

11 0 0

21 0 0

31 0 0

Loading...

Loading...