R8C/1A Group, R8C/1B Group 12. Interrupts

Rev.1.30 Dec 08, 2006 Page 86 of 315

REJ09B0252-0130

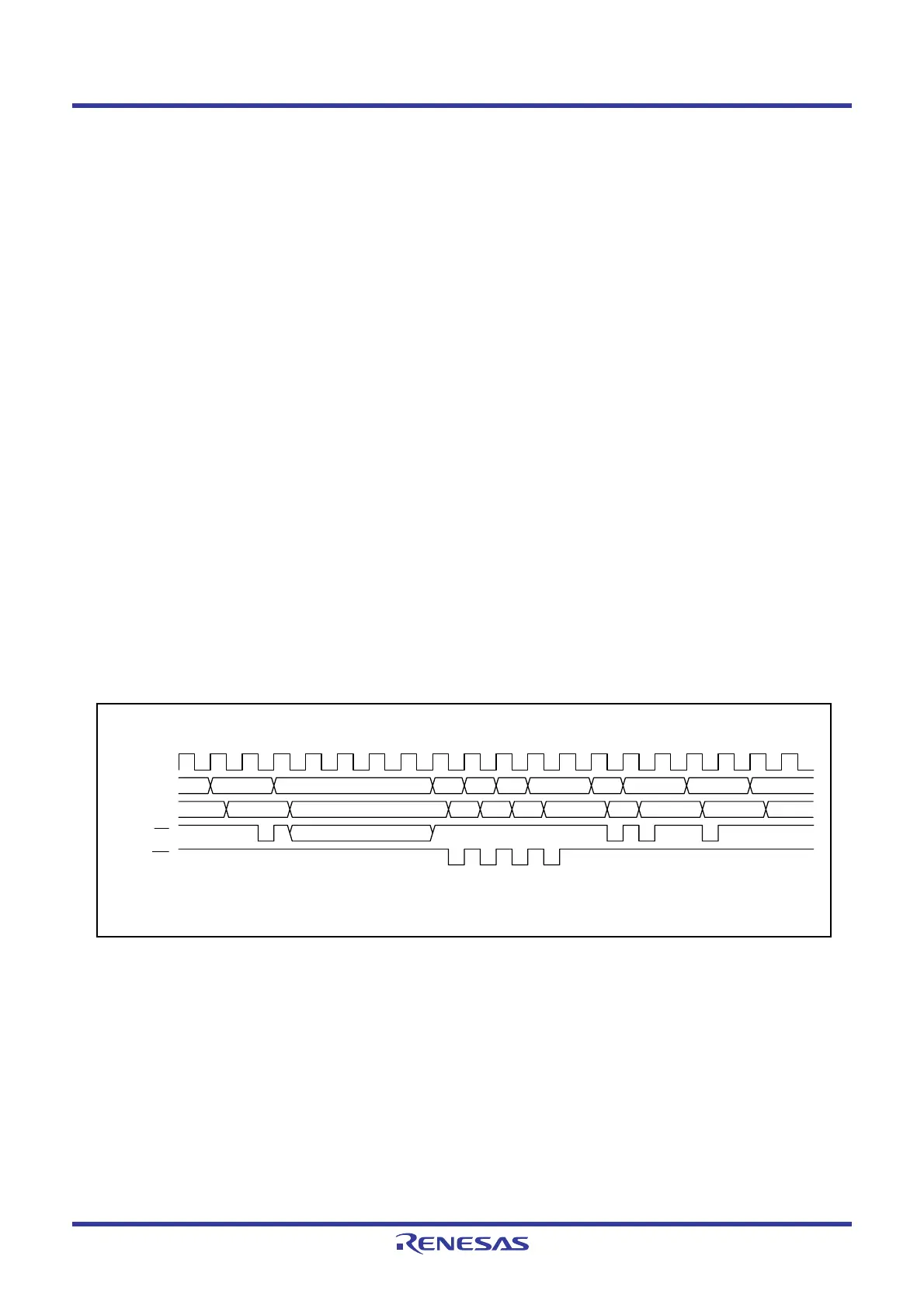

12.1.6.4 Interrupt Sequence

An interrupt sequence is performed between an interrupt request acknowledgement and interrupt routine

execution.

When an interrupt request is generated while an instruction is being executed, the CPU determines its interrupt

priority level after the instruction is completed. The CPU starts the interrupt sequence from the following cycle.

However, for the SMOVB, SMOVF, SSTR, or RMPA instruction, if an interrupt request is generated while the

instruction is being executed, the MCU suspends the instruction to start the interrupt sequence. The interrupt

sequence is performed as indicated below. Figure 12.5 shows the Time Required for Executing Interrupt

Sequence.

(1) The CPU gets interrupt information (interrupt number and interrupt request level) by reading address

00000h. The IR bit for the corresponding interrupt is set to 0 (interrupt not requested).

(2) The FLG register is saved to a temporary register

(1)

in the CPU immediately before entering the

interrupt sequence.

(3) The I, D, and U flags in the FLG register are set as follows:

The I flag is set to 0 (interrupts disabled).

The D flag is set to 0 (single-step interrupt disabled).

The U flag is set to 0 (ISP selected).

However, the U flag does not change state if an INT instruction for software interrupt number 32 to 63

is executed.

(4) The CPU’s internal temporary register

(1)

is saved to the stack.

(5) The PC is saved to the stack.

(6) The interrupt priority level of the acknowledged interrupt is set in the IPL.

(7) The starting address of the interrupt routine set in the interrupt vector is stored in the PC.

After the interrupt sequence is completed, instructions are executed from the starting address of the interrupt

routine.

NOTE:

1. This register cannot be used by user.

Figure 12.5 Time Required for Executing Interrupt Sequence

1234567891011 12 13 14 15 16 17 18 19 20

CPU clock

Address bus

Data bus

RD

WR

Address

0000h

Undefined

Undefined

Undefined

Interrupt

information

SP-2 SP-1 SP-4 SP-3 VEC VEC+1 VEC+2 PC

SP-2

contents

SP-1

contents

SP-4

contents

SP-3

contents

VEC

contents

VEC+1

contents

VEC+2

contents

The undefined state depends on the instruction queue buffer. A read cycle occurs when the instruction queue buffer is

ready to acknowledge instructions.

Loading...

Loading...