R8C/1A Group, R8C/1B Group 12. Interrupts

Rev.1.30 Dec 08, 2006 Page 87 of 315

REJ09B0252-0130

12.1.6.5 Interrupt Response Time

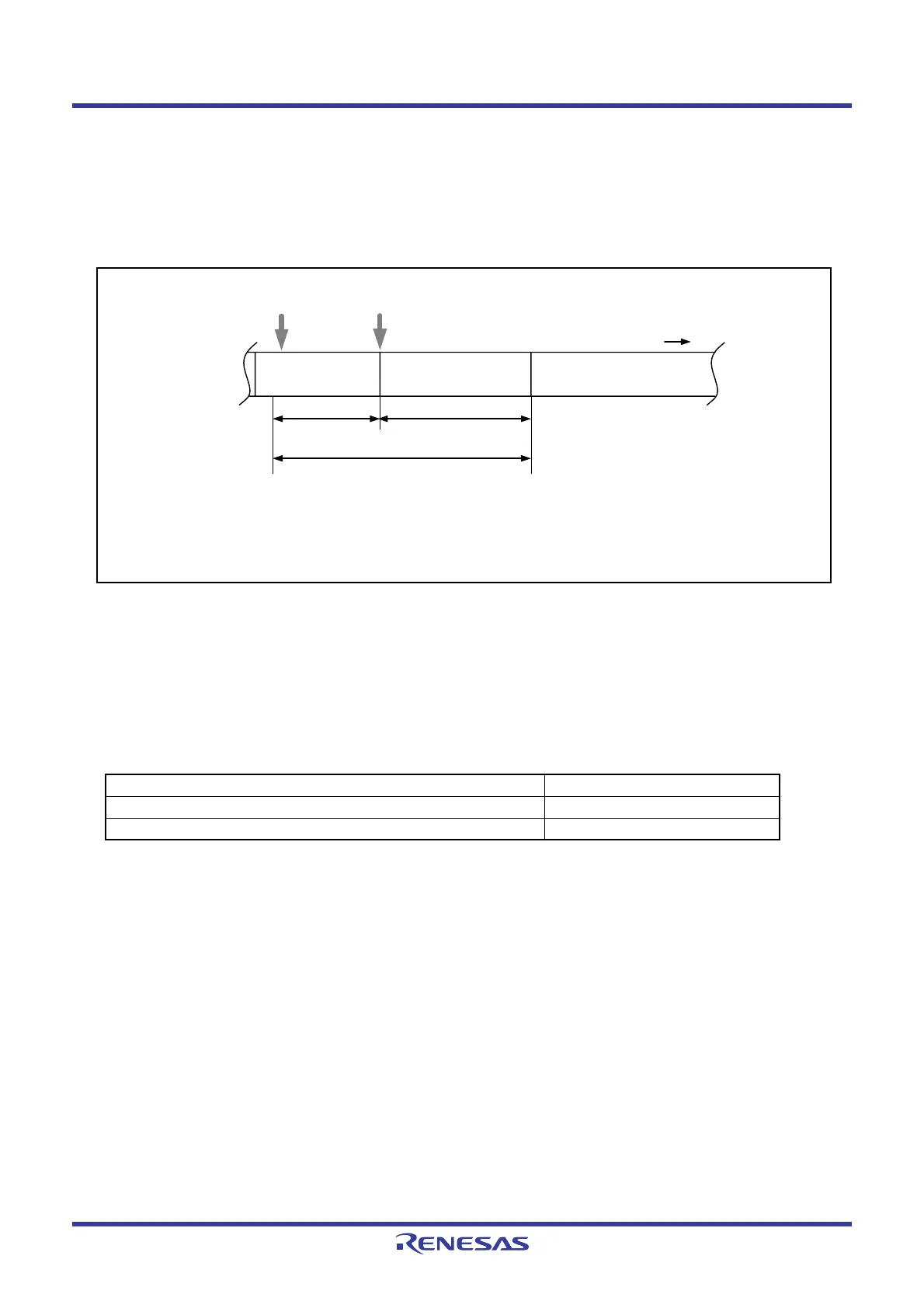

Figure 12.6 shows the Interrupt Response Time. The interrupt response time is the period between an interrupt

request generation and the execution of the first instruction in the interrupt routine. The interrupt response time

includes the period between interrupt request generation and the completion of execution of the instruction

(refer to (a) in Figure 12.6) and the period required to perform the interrupt sequence (20 cycles, see (b) in

Figure 12.6).

Figure 12.6 Interrupt Response Time

12.1.6.6 IPL Change when Interrupt Request is Acknowledged

When an interrupt request of a maskable interrupt is acknowledged, the interrupt priority level of the

acknowledged interrupt is set in the IPL.

When a software interrupt or special interrupt request is acknowledged, the level listed in Table 12.5 is set in

the IPL. Table 12.5 lists the IPL Value When a Software or Special Interrupt Is Acknowledged.

Table 12.5 IPL Value When a Software or Special Interrupt Is Acknowledged

Interrupt Source Value Set in IPL

Watchdog timer, oscillation stop detection, voltage monitor 2 7

Software, address match, single-step, address break Not changed

Interrupt request is generated. Interrupt request is acknowledged.

Instruction Interrupt sequence

Instruction in

interrupt routine

Time

(a) 20 cycles (b)

Interrupt response time

(a) Period between interrupt request generation and the completion of execution of an

instruction. The length of time varies depending on the instruction being executed.

The DIVX instruction requires the longest time, 30 cycles (assuming no wait states and

that a register is set as the divisor).

(b) 21 cycles for address match and single-step interrupts.

Loading...

Loading...