R8C/1A Group, R8C/1B Group 14. Timers

Rev.1.30 Dec 08, 2006 Page 117 of 315

REJ09B0252-0130

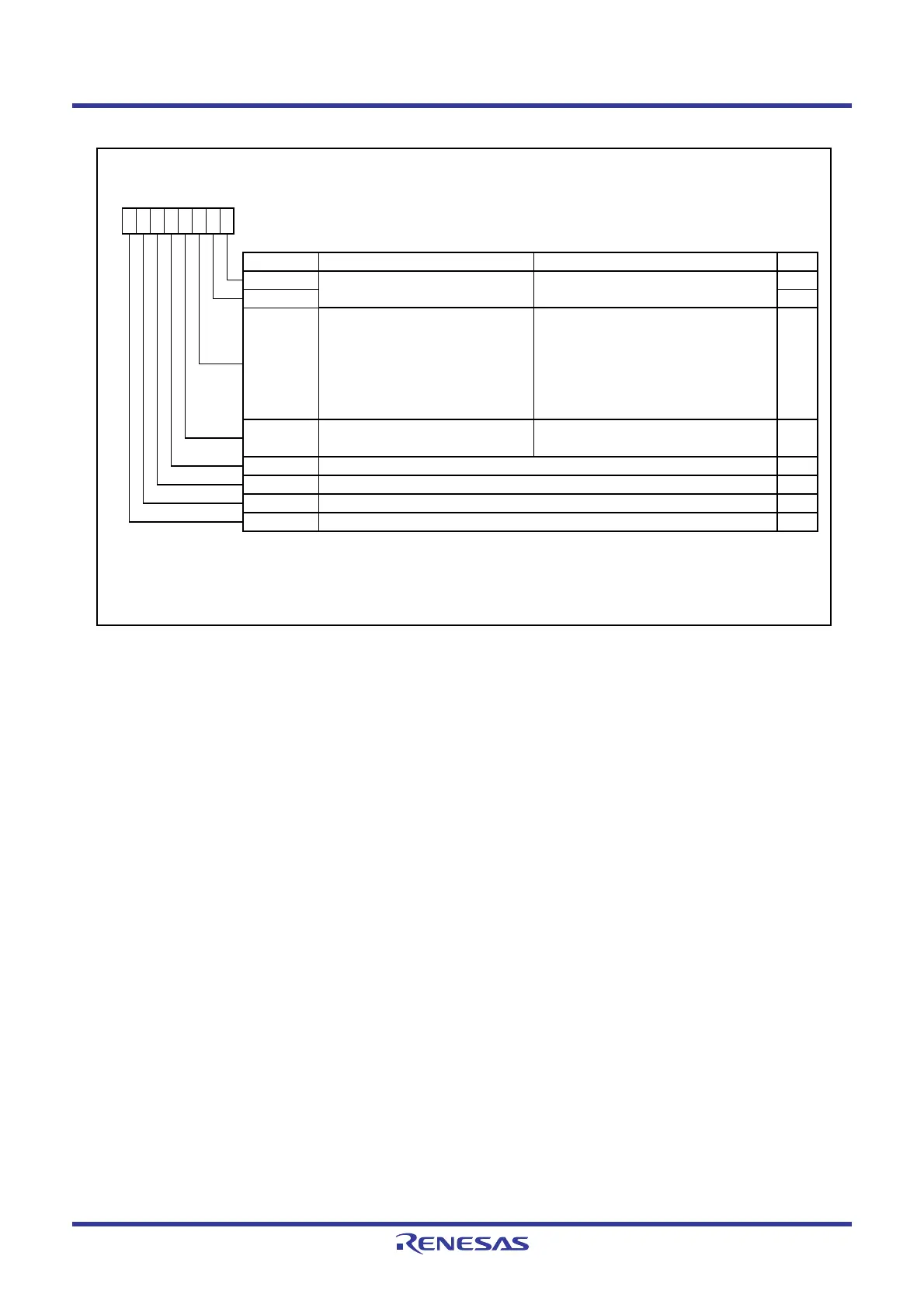

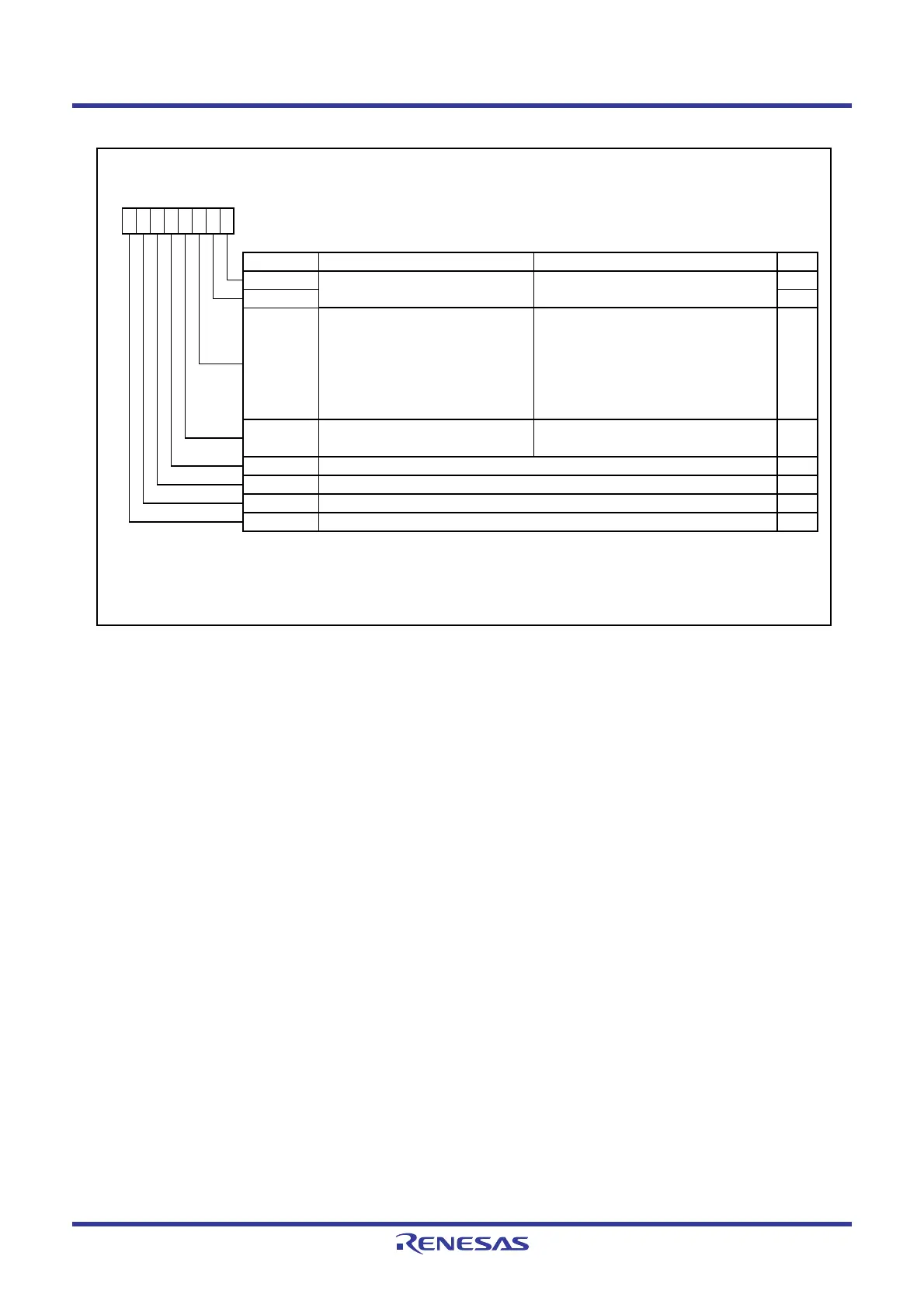

Figure 14.7 TXMR Register in Pulse Width Measurement Mode

Timer X Mode Register

Symbol Address After Reset

TXMR

008Bh 00h

Bit Symbol Bit Name Function RW

INT1

____

/CNTR0 signal

polarity sw itch bit

(1)

[INT1]

______

RW

0 : Rising edge

1 : Falling edge

NOTES :

1.

2.

11

The IR bit in the INT1IC register may be set to 1 (requests interrupt) w hen the R0EDG bit is rew ritten.

Refer to

12.5.5 Changing Interrupt Sources

.

R0EDG

RW

TXOCNT RW

TXMOD2 Set to 0 in pulse w idth measurement mode.

TXMOD0 RWOperating mode select bits 0, 1

b1 b0

1 1 : Pulse w idth measurement mode

TXMOD1 RW

b0

0000

b7 b6 b5 b4

Set to 0 in pulse w idth measurement mode.

RW

b3 b2

[CNTR0]

0 : Measures “L” level w idth

1 : Measures “H” level width

TXS

Timer X count start flag

(2)

0 : Stops counting.

1 : Starts counting.

b1

Refer to

14.1.6 Notes on Timer X

for precautions regarding the TXS bit.

Set to 0 in pulse w idth measurement mode.

Set to 0 in pulse w idth measurement mode.

RW

TXUND RW

TXEDG

Loading...

Loading...