R8C/1A Group, R8C/1B Group 14. Timers

Rev.1.30 Dec 08, 2006 Page 146 of 315

REJ09B0252-0130

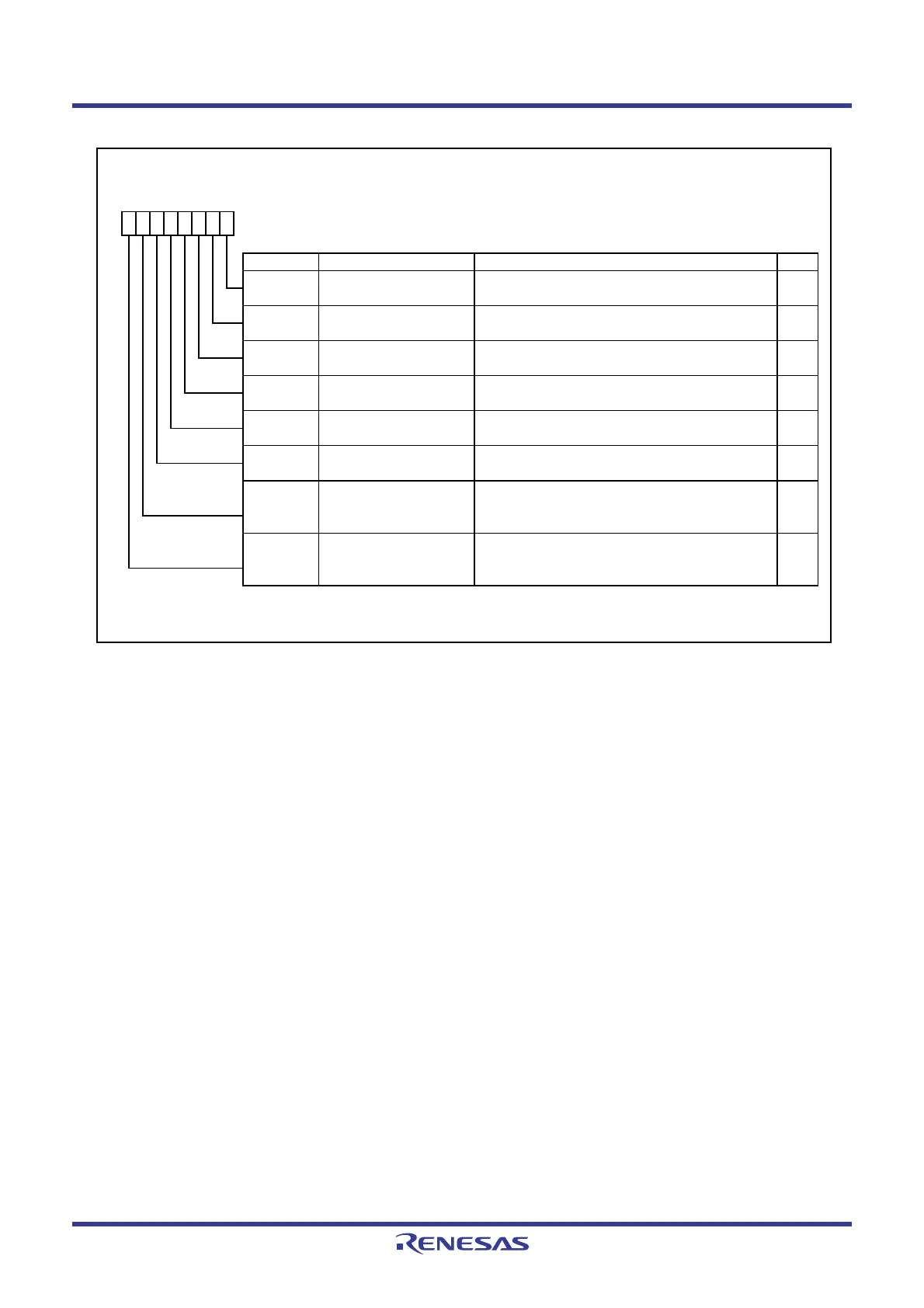

Figure 14.29 TCOUT Register

Timer C Output Control Register

(1)

Symbol Address After Reset

TCOUT

00FFh 00h

Bit Symbol Bit Name Function RW

NOTE :

1. Set the bits w hich are not used for CMP output to 0.

TCOUT7

TCOUT6

RW

CMP output enable bit 5

TCOUT5

CMP output enable bit 4 0 : Disables CMP output from CMP1_1.

1 : Enables CMP output from CMP1_1.

CMP output invert bit 1 0 : Does not invert CMP output from CMP1_0 to

CMP1_2.

1 : Inverts CMP output from CMP1_0 to CMP1_2.

b3 b2

0 : Disables CMP output from CMP0_2.

1 : Enables CMP output from CMP0_2.

b1 b0

TCOUT1

TCOUT0

b7 b6 b5 b4

RW

TCOUT2 RW

RW

CMP output enable bit 2

CMP output enable bit 0 0 : Disables CMP output from CMP0_0.

1 : Enables CMP output from CMP0_0.

CMP output enable bit 1 0 : Disables CMP output from CMP0_1.

1 : Enables CMP output from CMP0_1.

RW

TCOUT4

TCOUT3

CMP output enable bit 3 0 : Disables CMP output from CMP1_0.

1 : Enables CMP output from CMP1_0.

RW

0 : Disables CMP output from CMP1_2.

1 : Enables CMP output from CMP1_2.

RW

CMP output invert bit 0 0 : Does not invert CMP output from CMP0_0 to

CMP0_2.

1 : Inverts CMP output from CMP0_0 to CMP0_2.

RW

Loading...

Loading...