R8C/1A Group, R8C/1B Group 16. Clock Synchronous Serial Interface

Rev.1.30 Dec 08, 2006 Page 205 of 315

REJ09B0252-0130

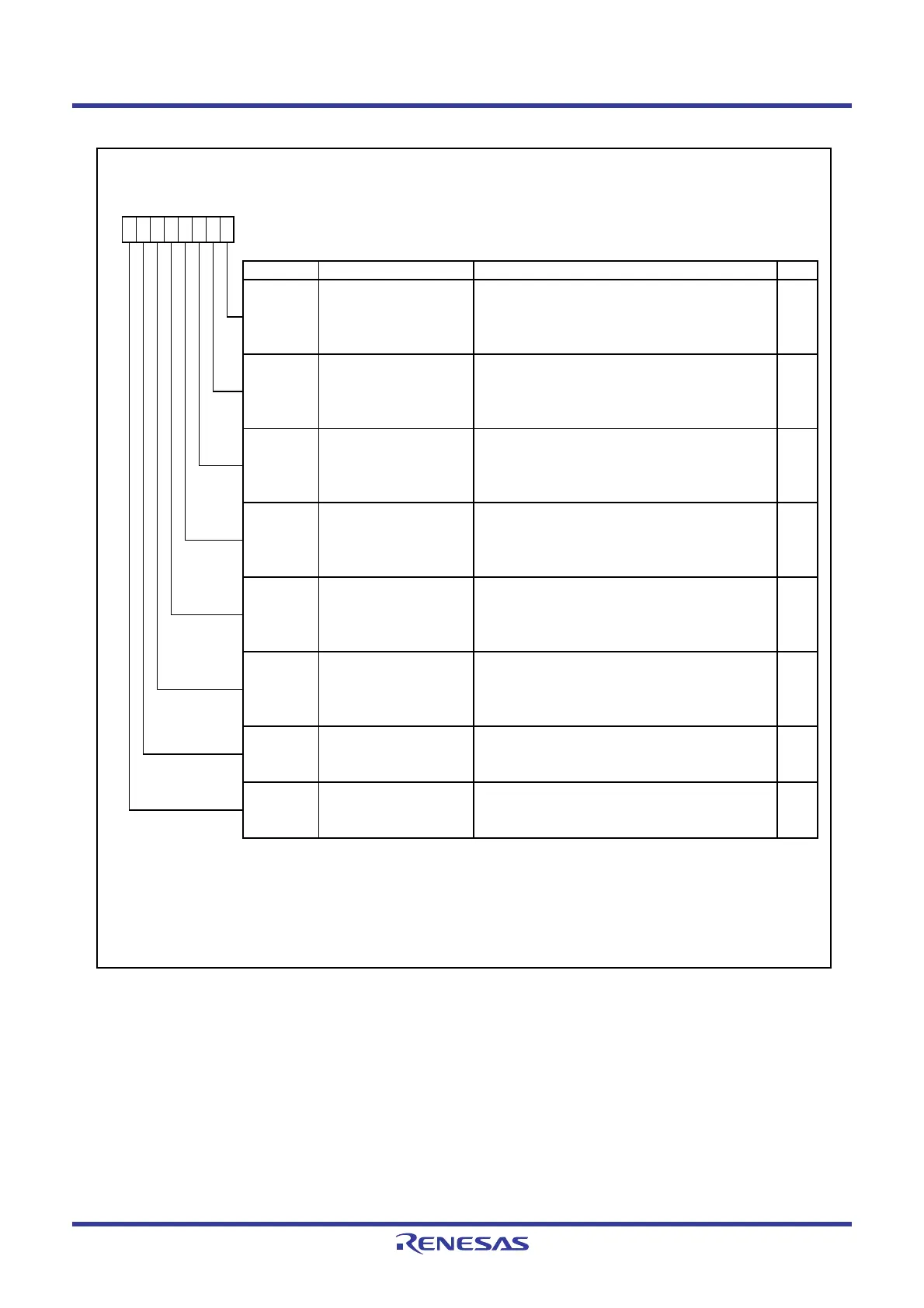

Figure 16.27 ICIER Register

IIC bus Interrupt Enable Register

(3)

Symbol Address After Reset

ICIER

00BBh 00h

Bit Symbol Bit Name Function RW

NOTES :

1.

2.

3.

Transmit acknow ledge

select bit

0 : 0 is transmitted as acknow ledge bit in

receive mode.

1 : 1 is transmitted as acknow ledge bit in

receive mode.

b0b3 b2 b1

NAKIE

b7 b6 b5 b4

ACKE

Transmit end interrupt

enable bit

STIE

ACKBT RW

RW

ROACKBR

RW

Receive acknow ledge bit 0 : Acknow ledge bit received from

receive device in transmit mode is set to 0.

1 : Acknow ledge bit received from

receive device in transmit mode is set to 1.

RIE

Receive interrupt enable

bit

0 : Disables receive data full and overrun

error interrupt request.

1 : Enables receive data full and overrun

error interrupt request.

(1)

RW

Acknow ledge bit judgment

select bit

0 : Value of receive acknow ledge bit is ignored

and continuous transfer is performed.

1 : When receive acknow ledge bit is set to 1,

continuous transfer is halted.

RW

Stop condition detection

interrupt enable bit

0 : Disables stop condition detection interrupt

request.

1 : Enables stop condition detection interrupt

request.

(2)

0 : Disables NACK receive interrupt request and

arbitration lost / overrun error interrupt request.

1 : Enables NACK receive interrupt request and

arbitration lost / overrun error interrupt request.

(1)

NACK receive interrupt

enable bit

Refer to

16.3.8.1 Accessing of Registers Associated with I

2

C bus Interface

for more information.

Set the STIE bit to 1 (enable stop condition detection interrupt request) w hen the STOP bit in the ICSR register is set

to 0.

0 : Disables transmit end interrupt request.

1 : Enables transmit end interrupt request.

RW

RW

An overrun error interrupt request is generated w hen the clock synchronous format is used.

TIE

Transmit interrupt enable

bit

0 : Disables transmit data empty interrupt request.

1 : Enables transmit data empty interrupt request.

TEIE

Loading...

Loading...