R8C/1A Group, R8C/1B Group 17. A/D Converter

Rev.1.30 Dec 08, 2006 Page 235 of 315

REJ09B0252-0130

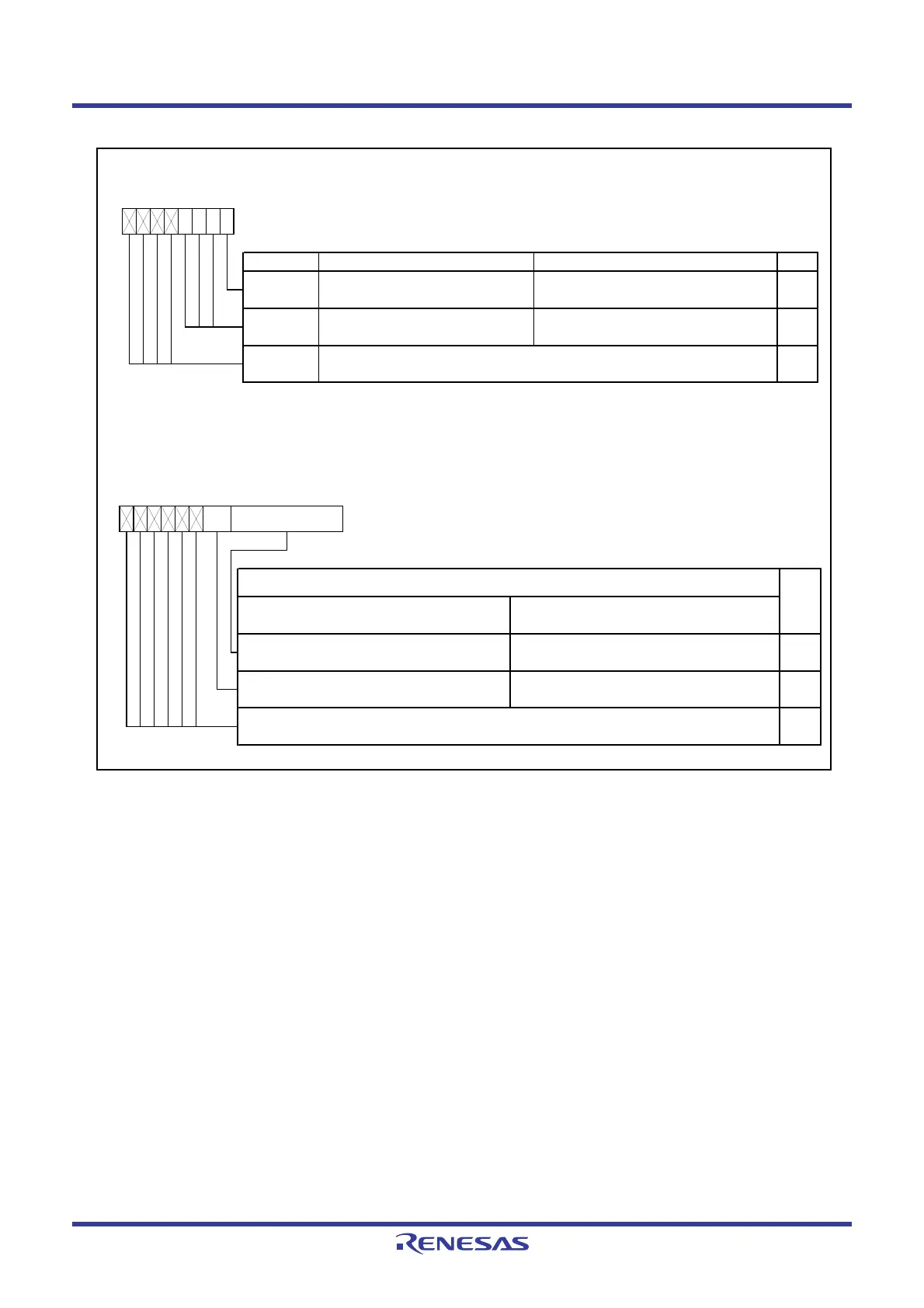

Figure 17.3 Registers ADCON2 and AD

A/D Control Register 2

(1)

Symbol Address After Reset

ADCON2 00D4h 00h

Bit Symbol Bit Name Function RW

NOTE :

1.

0 : Without sample and hold

1 : With sample and hold

RW

When the ADCON2 register is rew ritten during A/D conversion, the conversion result is undefined.

SMP

A/D conversion method select bit

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

—

(b7-b4)

—

—

(b3-b1)

RW

Reserved bits Set to 0.

b7 b6 b5 b4

0

b3 b2 b1 b0

00

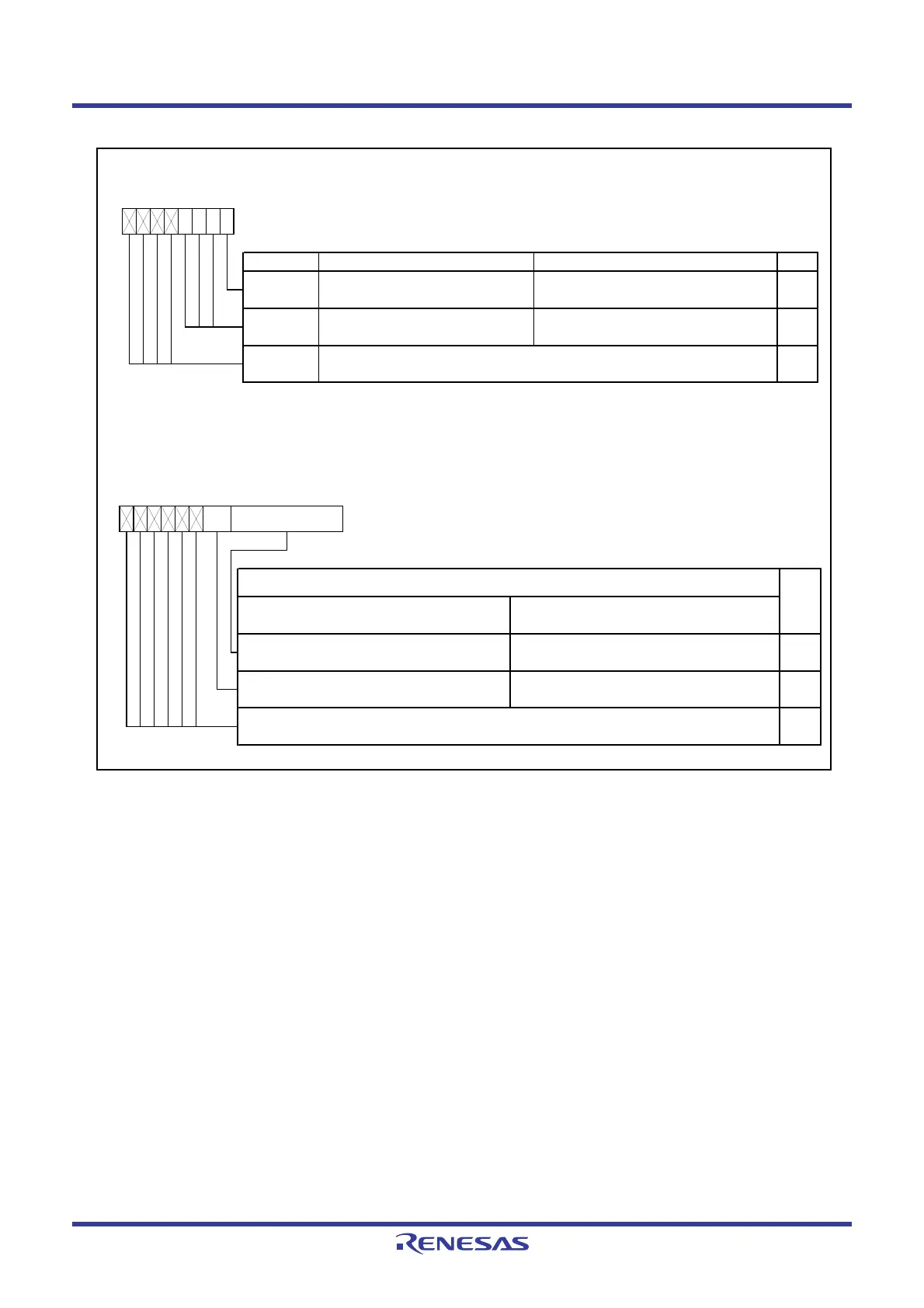

/D Registe

Symbol Address After Reset

AD

00C1h-00C0h Undefined

(b15)

b7

(b8)

b0

b0b7

RO

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

—

2 high-order bits in A/D conversion result When read, the content is undefined.

Function

RO

RW

When BITS bit in ADCON1 register is set to 1

(10-bit mode).

When BITS bit in ADCON1 register is set to 0

(8-bit mode).

8 low -order bits in A/D conversion result A/D conversion result

Loading...

Loading...