) enables sampling more often.

However, increasing C

ext

limits the frequency bandwidth of measurement signal (increasing

the “external” timing constant R

in

. C

ext

).

The formulas below show how to choose the optimal C

ext

value: signal bandwidth in

correlation with sample time. Signal bandwidth is characterized by an “external” timing

constant, so optimal solution is to charge C

ext

during t

C

:

After simplification we obtain the final formula for optimal C

ext

:

and the corresponding waiting time between conversions:

Practically the firmware must not program the ADC in continuous mode but only in single

mode and must ensure that there will be a time gap between conversions with duration

equal to t

C

. This adding of waiting time is the software change which must be applied

together with the hardware change (adding an external capacitor C

ext

).

Without implementation of t

C

waiting time in software (for instance, running a conversion just

after the first one) the external capacitor C

ext

will be cyclically charged from the C

sh

capacitor. After a lot of cycles the voltage on C

ext

will reach a quite high error value (as

previously shown in Figure 36).

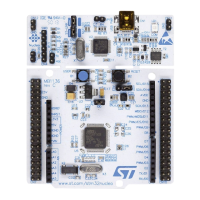

A practical example of implementation for STM32L1 ADC is shown below:

C

sh

= 16 pF ..... ADC property

R

in

= 150 kΩ ..... signal source property

Loading...

Loading...