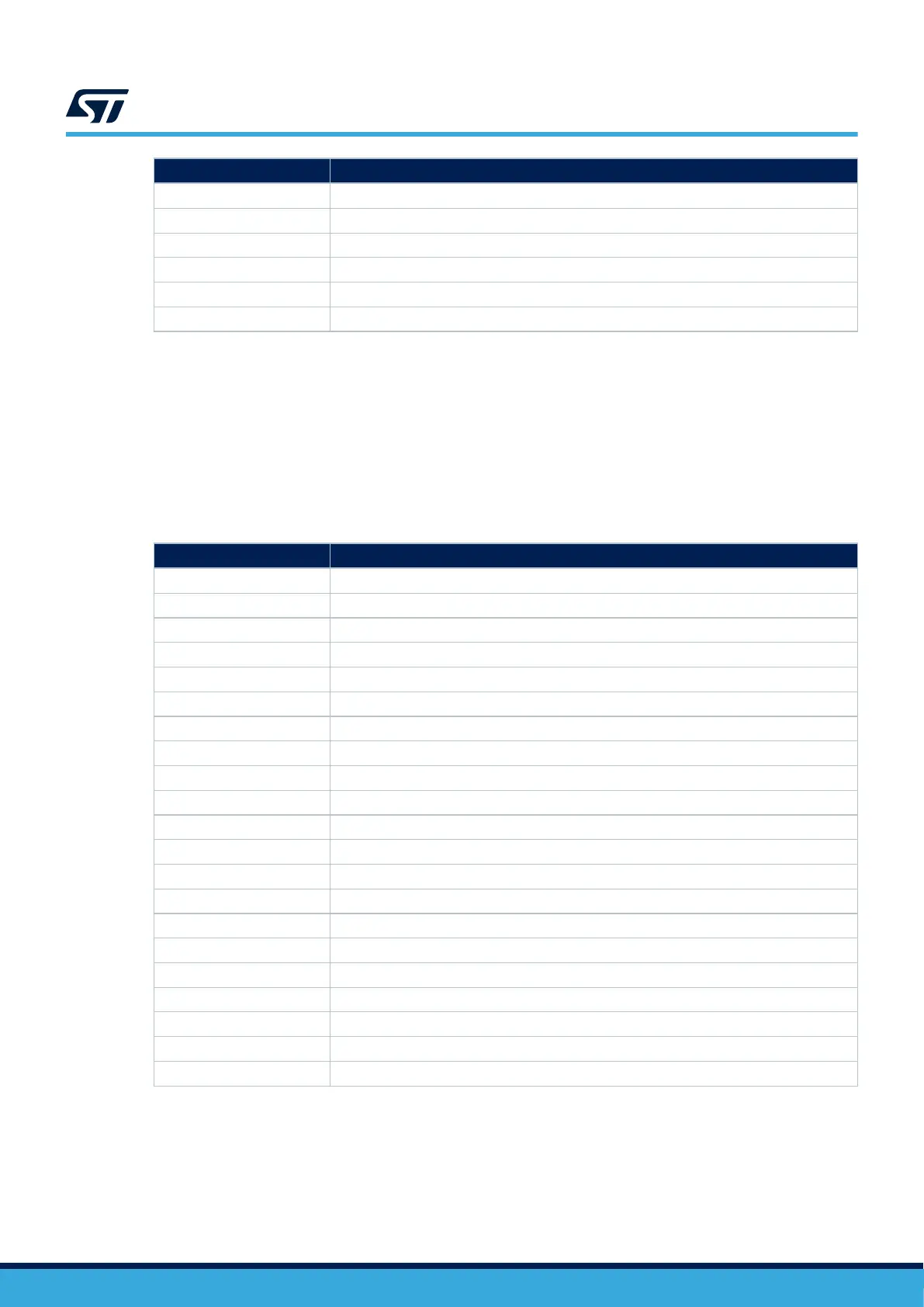

PIO Configuration

PF15 ADC2 (UCPD.ADC2) - optionally used

PA12 HS_P (USBC.HS_P)

PA11 HS_N (USBC.HS_N)

PG1 VBUS_SENSE (VBUS_SENSE)

PA15 CC1 (UCPD.CC1) - not used

PB15 CC2 (UCPD.CC2) - not used

12.3 Hexadeca‑SPI PSRAM memory

The APS512XXN-OBR-BG APMemory DDR Octal SPI PSRAM has the following characteristics: 512 Mbit, x8x16,

1v8, 200 MHz, DDR and PASR mode. The PSRAM is managed through the Hexadeca‑SPI interface.

The MB1829 main board supports at least 160 MHz DDR setting. To reach these performances, the HSLV feature

of MCU is activated for the Hexadeca‑SPI interface.

The embedded footprint might also be compatible with other references in the BGA24 package, check the

compatibility of the memory datasheet versus MB1829 schematics.

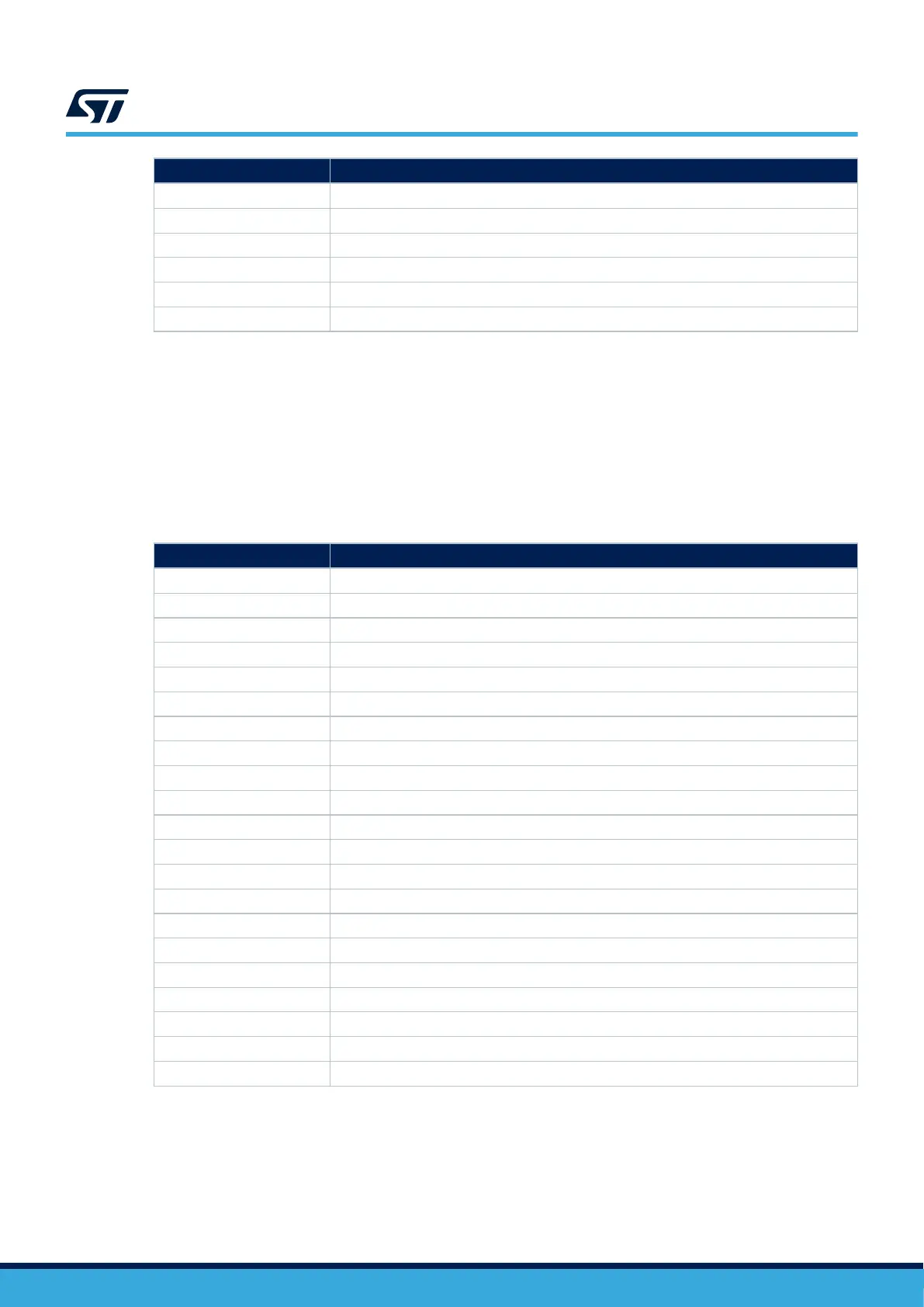

Table 12. Hexadeca‑SPI PSRAM I/O interface

PIO Configuration

PH9 NCS (HEXASPI1.NCS)

PI3 CLK (HEXASPI1.CLK)

PI2 DQS0 (HEXASPI1.DQS0)

PH10 IO0 (HEXASPI1.IO0)

PH11 IO1 (HEXASPI1.IO1)

PH12 IO2 (HEXASPI1.IO2)

PH13 IO3 (HEXASPI1.IO3)

PH14 IO4 (HEXASPI1.IO4)

PH15 IO5 (HEXASPI1.IO5)

PI0 IO6 (HEXASPI1.IO6)

PI1 IO7 (HEXASPI1.IO7)

PI4 NCLK - not used/not accessible

PI8 DQS1 (HEXASPI1.DQS1)

PI9 IO8 (HEXASPI1.IO8)

PI10 IO9 (HEXASPI1.IO9)

PI11 IO10 (HEXASPI1.IO10)

PI12 IO11 (HEXASPI1.IO11)

PI13 IO12 (HEXASPI1.IO12)

PI14 IO13 (HEXASPI1.IO13)

PI15 IO14 (HEXASPI1.IO14)

PJ0 IO15 (HEXASPI1.IO15)

UM2967

Hexadeca‑SPI PSRAM memory

UM2967 - Rev 1

page 31/68

Loading...

Loading...