DocID026079 Rev 3 77/102

STM32F038x6 Electrical characteristics

79

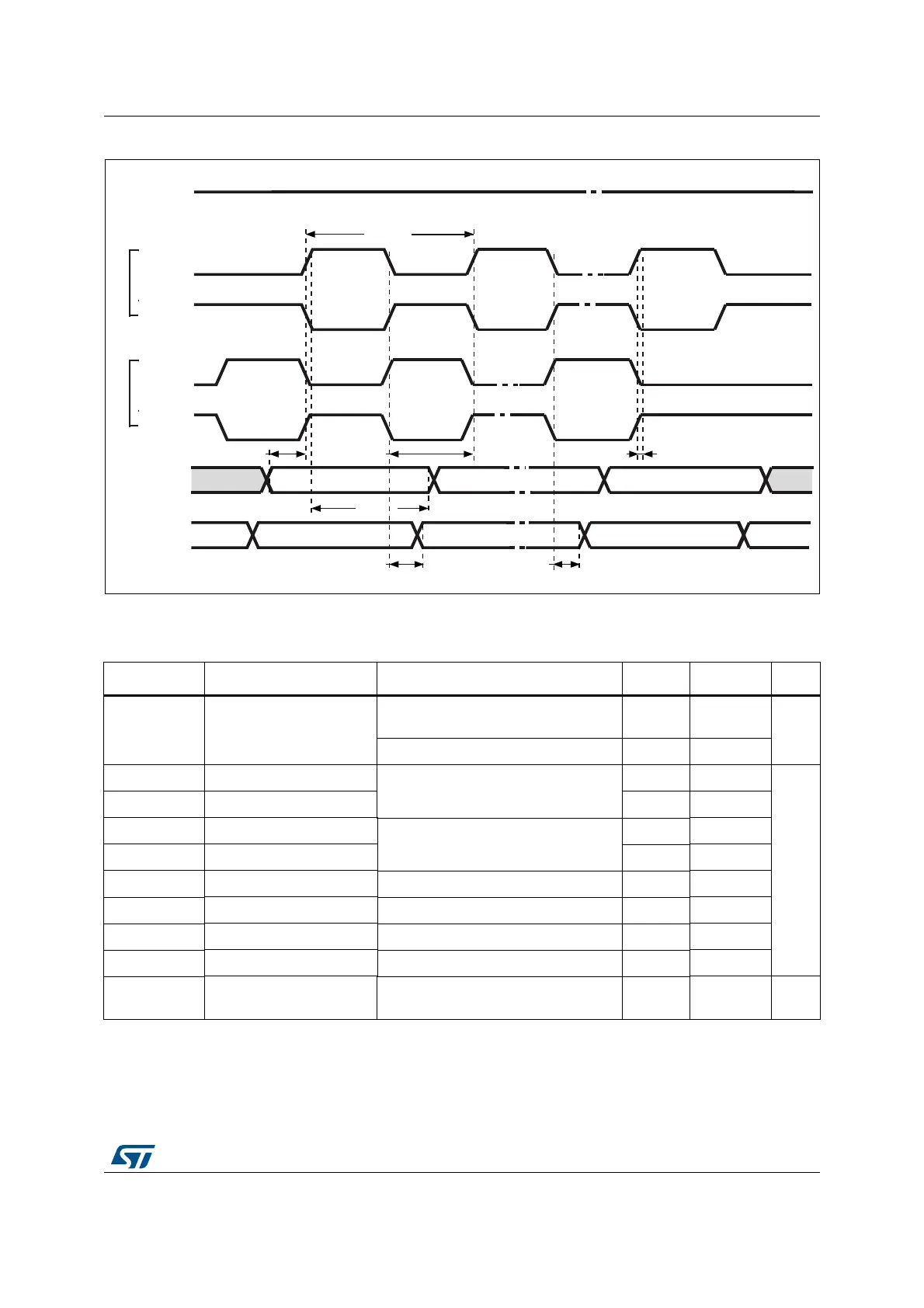

Figure 27. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3 V

DD

and 0.7 V

DD

.

DLF

6&.2XWSXW

&3+$

026,

287387

0,62

,13 87

&3+$

/6%287

/6%,1

&32/

&32/

% , 7287

166LQSXW

W

F6&.

W

Z6&.+

W

Z6&./

W

U6&.

W

I6&.

W

K0,

+LJK

6&.2XWSXW

&3+$

&3+$

&32/

&32/

W

VX0,

W

Y02

W

K02

06%,1

%,7,1

06%287

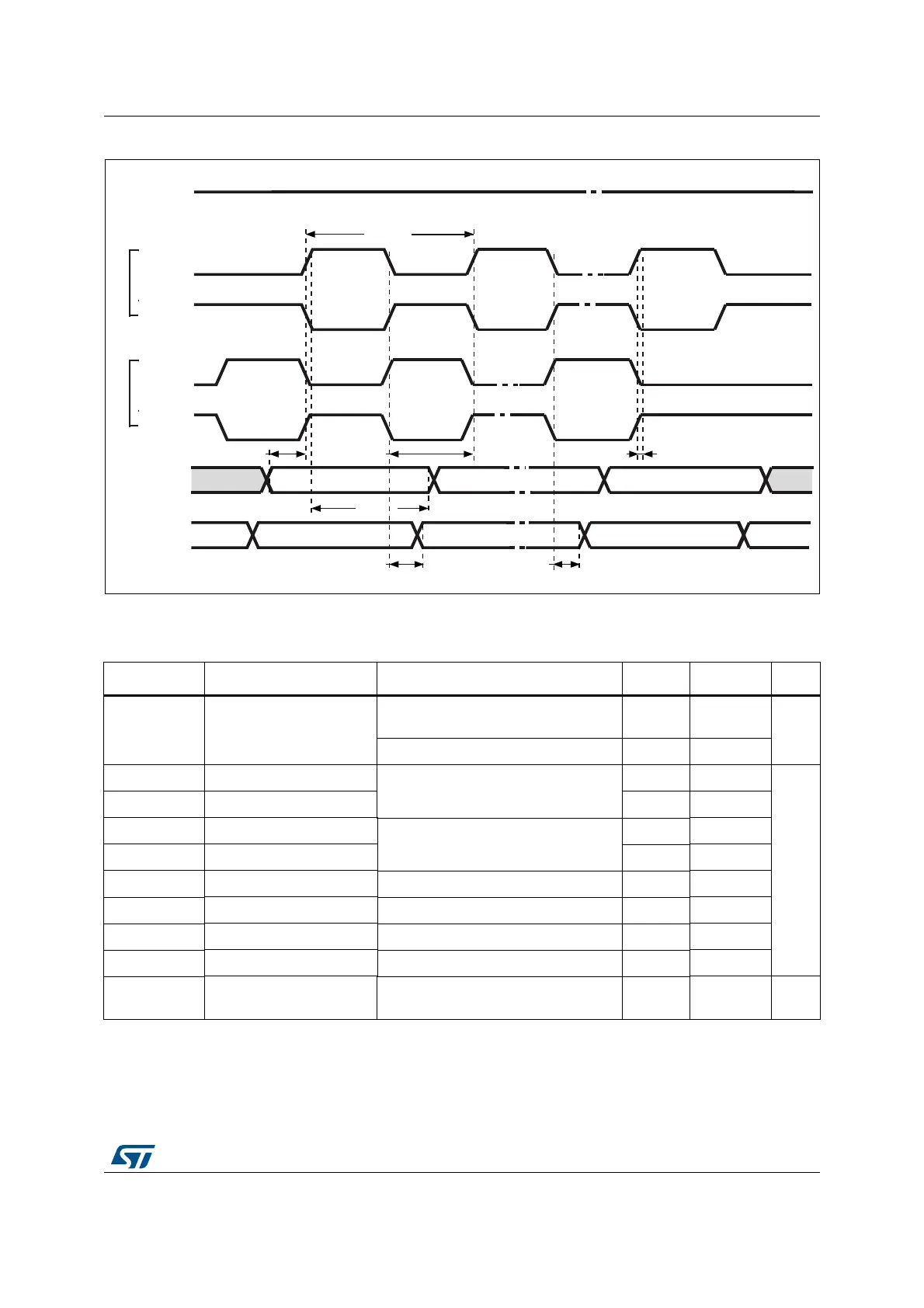

Table 59. I

2

S characteristics

(1)

Symbol Parameter Conditions Min Max Unit

f

CK

1/t

c(CK)

I

2

S clock frequency

Master mode (data: 16 bits, Audio

frequency = 48 kHz)

1.597 1.601

MHz

Slave mode 0 6.5

t

r(CK)

I

2

S clock rise time

Capacitive load C

L

= 15 pF

-10

ns

t

f(CK)

I

2

S clock fall time - 12

t

w(CKH)

I

2

S clock high time

Master f

PCLK

= 16 MHz, audio

frequency = 48 kHz

306 -

t

w(CKL)

I

2

S clock low time 312 -

t

v(WS)

WS valid time Master mode 2 -

t

h(WS)

WS hold time Master mode 2 -

t

su(WS)

WS setup time Slave mode 7 -

t

h(WS)

WS hold time Slave mode 0 -

DuCy(SCK)

I

2

S slave input clock duty

cycle

Slave mode 25 75 %

Loading...

Loading...