User manual 9-2

DSC/DSCT Series

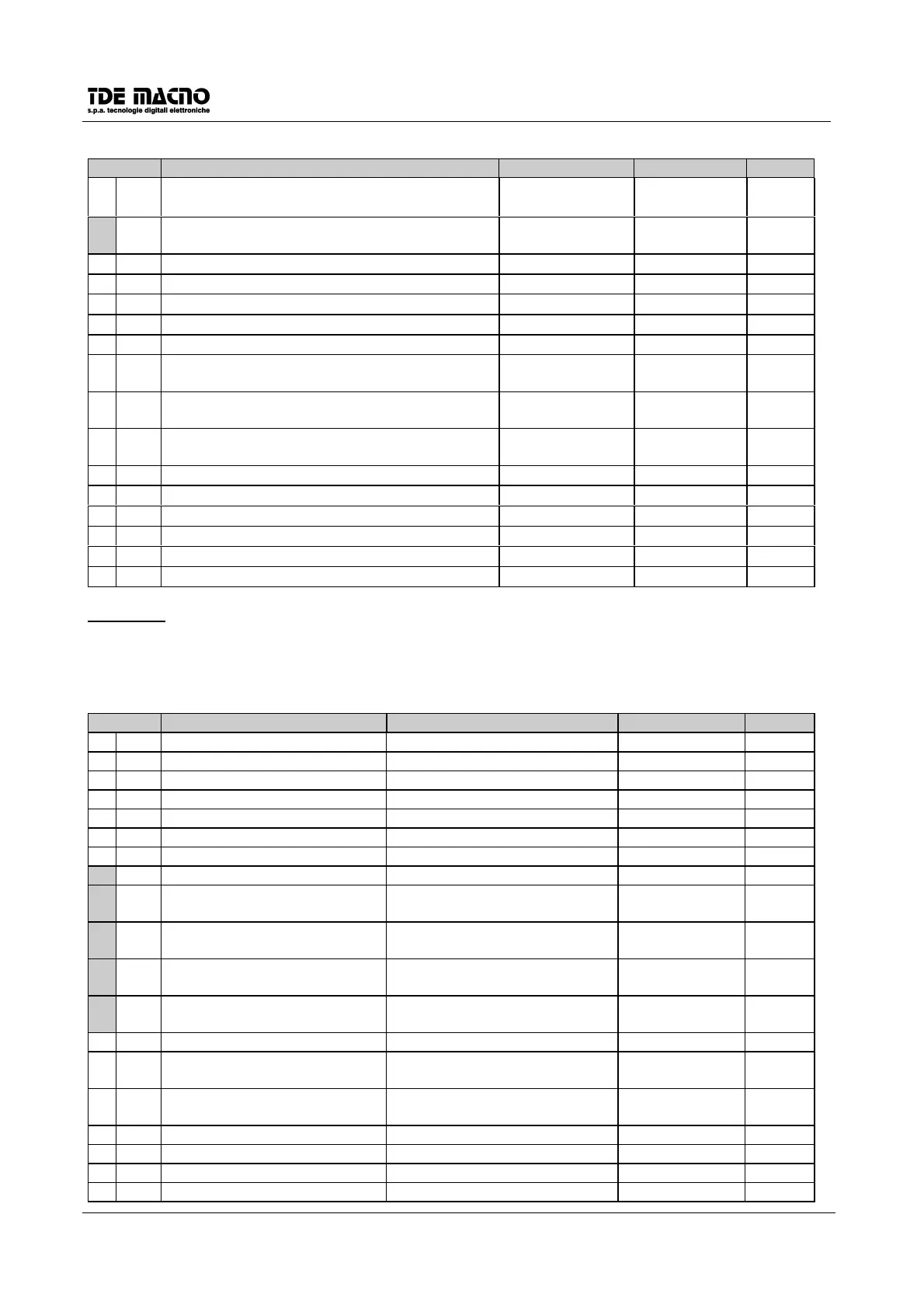

SECT. DESCRIPTION FIELD DEFAULT Notes

P 58 Motor inductance in mH x rated motor current

20÷280

(DSC)

30÷450

(DSCT)

70

(DSC)

100

(DSCT)

r

P 60 External voltage reference corresponding to

the maximum motor speed (mV)

2500÷10000

10000 r

P 61 Encoder frequency reference coefficient

0÷16383

4096

P 80 TDE reserved parameter access key

0÷9999

-n

P 81 Analogue ref. correction coefficient

50.0%÷199.0%

100.0% t

P 83 Drive rated correction in % of the current limit

20.0%÷100.0%

50.0% t

P 84 Drive limit reenter time constant

1.0÷10.0s.

2.5s. t

P 85 VNS not stabilised voltage measurement coeff.

2500÷10000

4930

(DSC)

9015

(DSCT)

t

P 86 DC bus minimum voltage

180.0÷400.0V

220.0V

(DSC)

380.0V

(DSCT)

t

P 87 DC bus maximum voltage

200.0÷600.0V

410.0V

(DSC)

800.0V

(DSCT)

t

P 88 DAC_V coefficient for fs speed output

800÷1250

1000 t

P 89 Minimum flyback voltage (24V)

75.0%÷95.0%

85.0% t

P 90 Maximum flyback voltage (24V)

100.0%÷120.0%

110.0% t

P 91 Current reference offset

÷100.0%

0t

P 92 Current regulator delay compensation

0÷1000 ÷sec

200 t

P 99 Customer code number

0÷9999

95 t

On request, we can change the default value (95) of parameter

P99

, which sets the customer code number

(

P50

), to customise the drive.

Bold

P

indicates the most used parameters that had to be setted in a new installation.

9.2. CONNECTIONS

(Note: n = off-line , r = reserved to the customer, t = TDE-reserved)

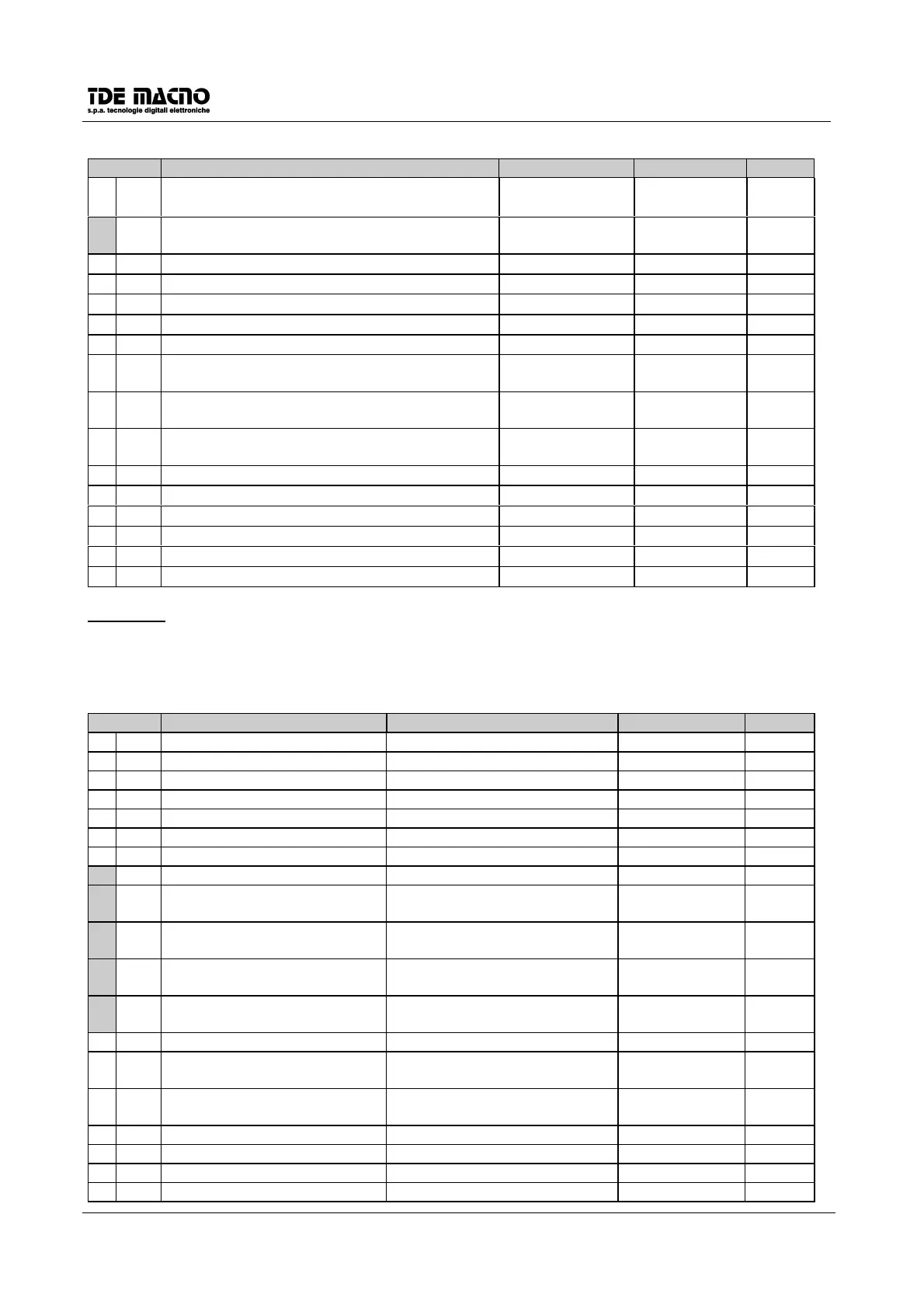

CON. DESCRIPTION FIELD DEFAULT Notes

c 1 Logic input 1 meaning 1-8 (see sect. 7.1) 1 (

TQ.EN

)r

c 2 Logic input 2 meaning 0 (see sect. 7.1) 0 (

DR.RUN

)r

c 3 Logic input 3 meaning 1-8 (see sect. 7.1) 3 (

REF1EN

)r

c 4 Logic input 4 meaning 1-8 (see sect. 7.1) 8 (

Fault Reset

)r

c 5 Logic input 5 meaning 1-8 (see sect. 7.1) 2 (

EXT.EN

)r

c 7 Logic output 1 meaning 0-9 (see sect. 7.2) 0 (

DR.READY

)r

c 8 Logic output 2 meaning 0-9 (see sect. 7.2) 3 (

DR.ONLINE

)r

c 9 Speed reference inversion 0 (not inverted) 1(inverted) 0 r

c 10 Simulated encoder channel B

inversion

0 (not inverted) 1(inverted) 0 r

c 11 Choice pulse/rev. resolver for

simulated encoder

0-7 (see sect. 7.4) 4 (512

PPR

)r

c 12 Choice zero simulated encoder

phase

0-3 (see sect. 7.4) 0 r

c 13 Meaning programmable

analogue output

0-3 (see sect. 7.3) 1

c 14 Choice external reference 0 (analogue) 1 (frequency) 0 r

c 19 Exclusion alarms

A3,A4,A5,A9,A7

0-31 (see sect. 8.2) 0 r

c 20 Exclusion integral on speed

regulator

0 (not excluded) 1 (excluded) 0 n

c 21 Software on line 0(stop) 1(run) 1

c 22 Parallel bit to REF1 0(OFF) 1(ON) 0

c 23 Parallel bit to REF2 0(OFF) 1(ON) 0

c 24 Parallel bit to LS1 0(OPEN) 1(CLOSED) 1

Loading...

Loading...