52

8303460000 Rev A IA672-04-01-Rev. I

11.8.8. Read the Standard Event Status Event Register

This is a basic status and fault register that was first defined in IEEE-488.2. It is an

event register, which means bits are set to “1” when a condition occurs and they are

not cleared until the register value is read using the *ESR? query or the *CLS

command

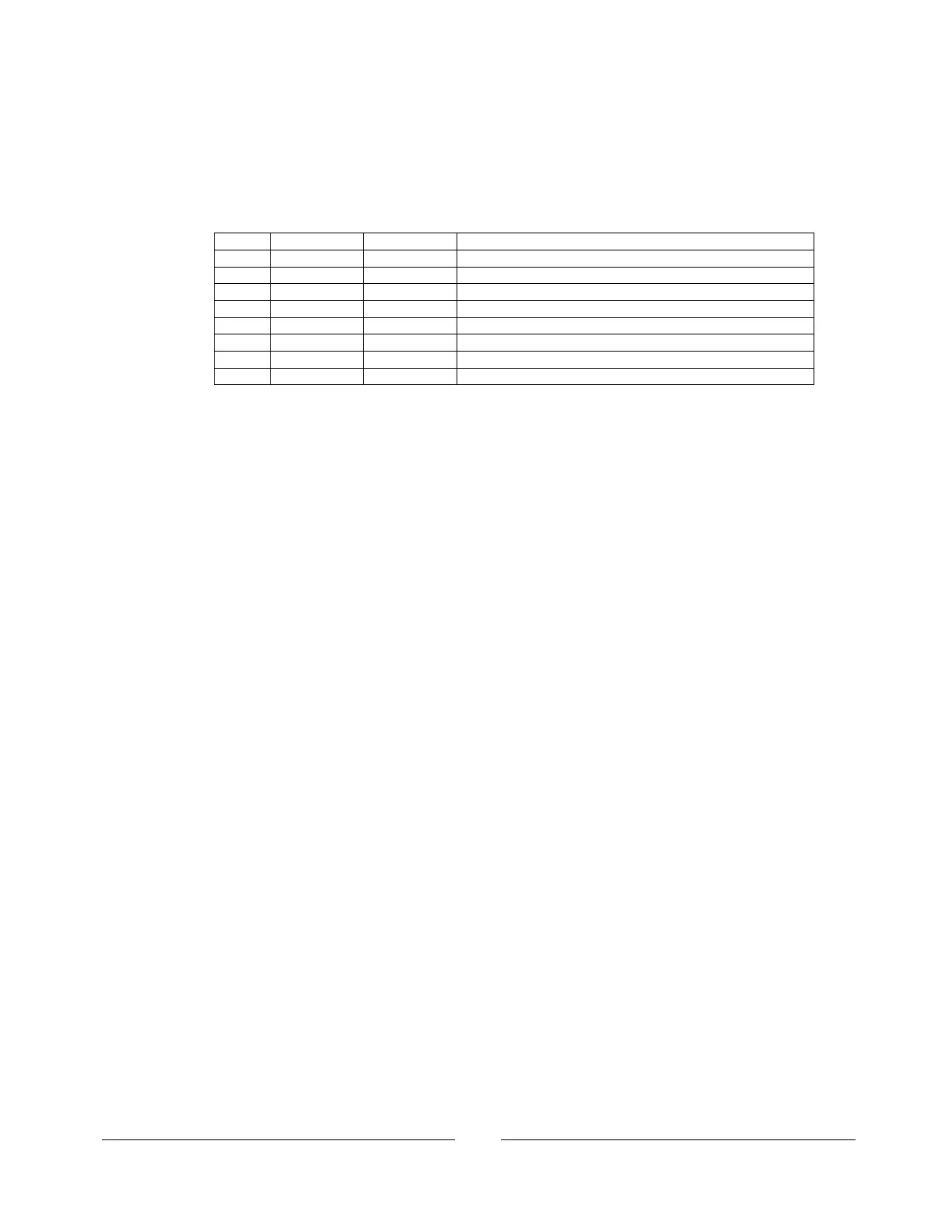

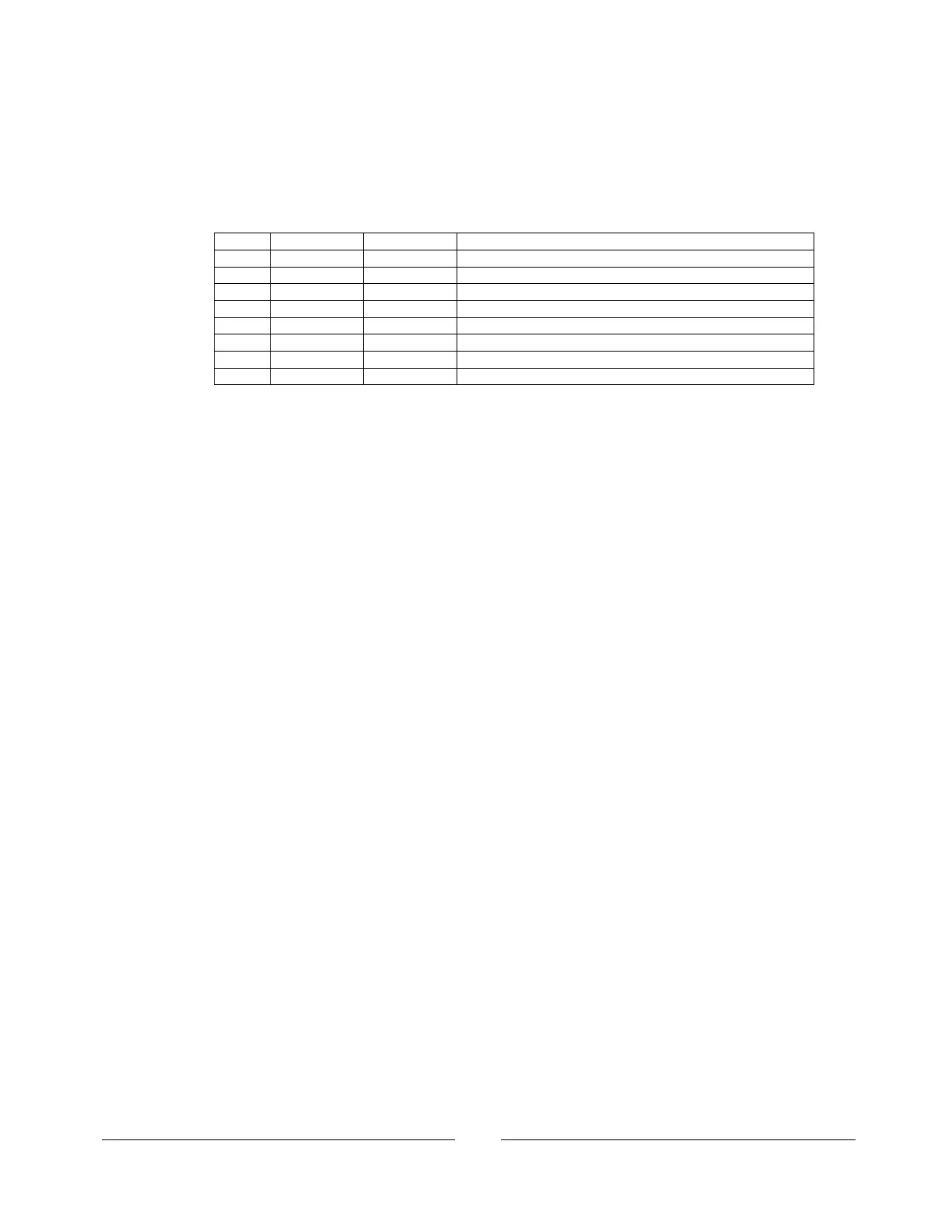

These are the bit assignments of the ESR register:

Operation complete. See section 11.8.10

Query error (response not read)

Device dependant error (fault shut-down)

Execution error (could not execute command)

Command error (invalid command received)

Power On. Set once when power is switched on.

Syntax: *ESR ?

Response: <nnn>, a number from 0 to 255

Example: 32 (an illegal command was received)

11.8.9. Set the Standard Event Status Enable Register

When one or more bits in the Standard Event Status Event Register (*ESR, see

above) are set, a bit can be set in the Status Byte (*STB, see section 11.8.6). This is

done by setting bits in the enable register.

Syntax: *ESE <nnn>

Parameter: <nnn> is a number from 0 to 255. The bit assignments are the

same as the *ESR, in the table above

Example: *ESE 60 will cause bit 5 in the Status Byte to be set if there is a

query error, fault shut-down, execution error or a

command error

Query: *ESE? will return 60 in the example

11.8.10. Enable the Operation Complete

This command will cause bit 0 of the Standard Event Status Register to go to 1

when all pending commands are completed. Because of the Genesys™ power supply

architecture, this bit will go to 1 when the *OPC is received, even if the output is in

transition because of a prior command.

Syntax: *OPC

11.8.11. Read the Operation Complete

This query will read back if all pending operations are completed. This query will

always return 1, even if the DC output is in transition because of a prior command.

Syntax: *OPC ?

Loading...

Loading...