RF Core

www.ti.com

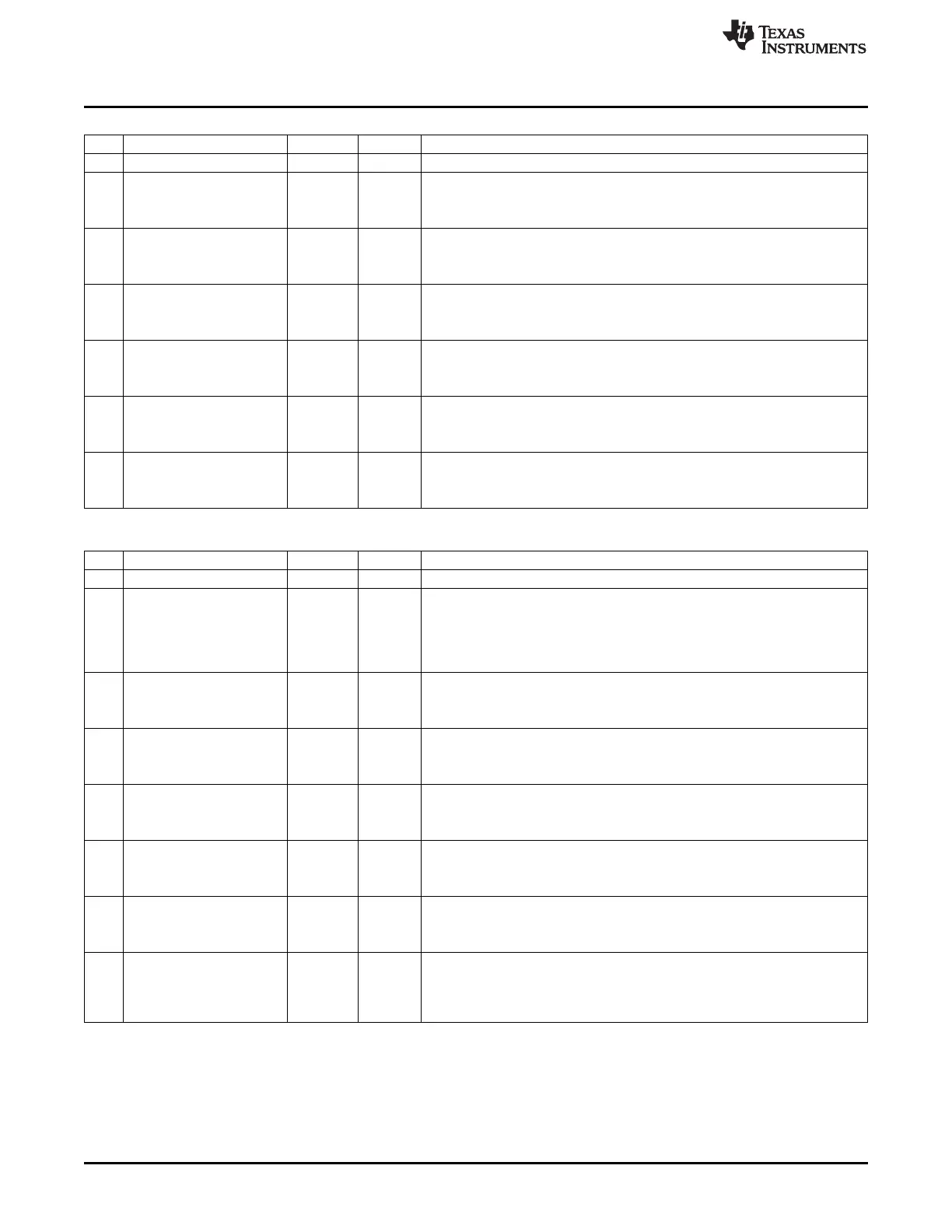

RFIRQF1 (0x91) RF Interrupt Flags

Bit Name Reset R/W Description

7:6 – 00 R0 Reserved. Read as 0

5

CSP_WAIT

0 R/W0 Execution continued after a wait instruction in CSP.

0: No interrupt pending

1: Interrupt pending

4

CSP_STOP

0 R/W0 CSP has stopped program execution.

0: No interrupt pending

1: Interrupt pending

3

CSP_MANINT

0 R/W0 Manual interrupt generated from CSP.

0: No interrupt pending

1: Interrupt pending

2

RFIDLE

0 R/W0 Radio state machine has entered the idle state.

0: No interrupt pending

1: Interrupt pending

1

TXDONE

0 R/W0 A complete frame has been transmitted.

0: No interrupt pending

1: Interrupt pending

0

TXACKDONE

0 R/W0 An acknowledgement frame has been completely transmitted.

0: No interrupt pending

1: Interrupt pending

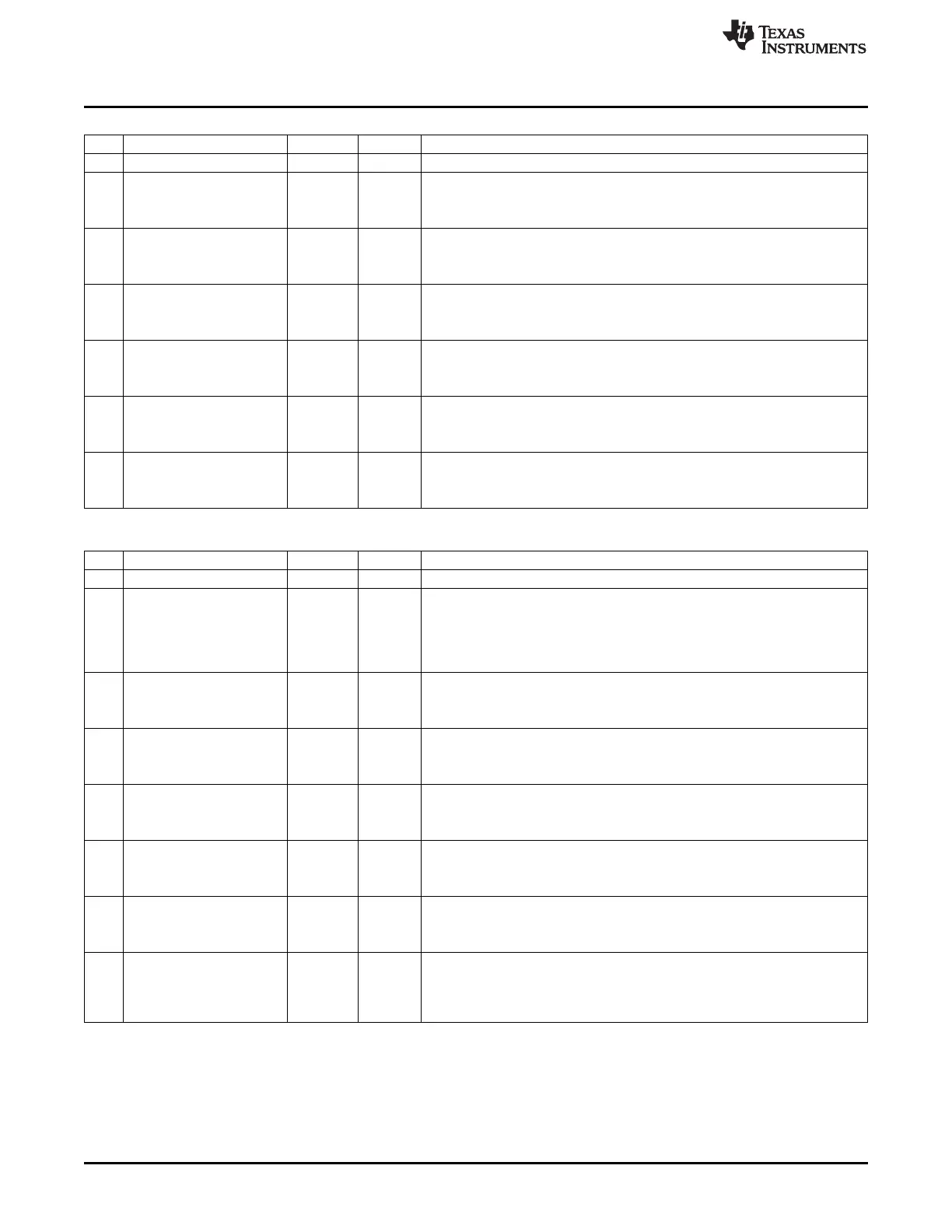

RFERRF (0xBF) – RF Error Interrupt Flags

Bit Name Reset R/W Description

7 – 0 R0 Reserved. Read as 0

6

STROBEERR

0 R/W0 A command strobe was issued at a time it could not be processed. Triggered if

trying to disable radio when already disabled, or when trying to do a SACK,

SACKPEND, or SNACK command when not in active RX.

0: No interrupt pending

1: Interrupt pending

5

TXUNDERF

0 R/W0 TXFIFO underflowed

0: No interrupt pending

1: Interrupt pending

4

TXOVERF

0 R/W0 TXFIFO overflowed

0: No interrupt pending

1: Interrupt pending

3

RXUNDERF

0 R/W0 RXFIFO underflowed

0: No interrupt pending

1: Interrupt pending

2

RXOVERF

0 R/W0 RXFIFO overflowed

0: No interrupt pending

1: Interrupt pending

1

RXABO

0 R/W0 Reception of a frame was aborted.

0: No interrupt pending

1: Interrupt pending

0

NLOCK

0 R/W0 Frequency synthesizer failed to achieve lock after timeout, or lock is lost during

reception. Receiver must be restarted to clear this error situation.

0: No interrupt pending

1: Interrupt pending

222

CC253x Radio SWRU191C–April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...