www.ti.com

Registers

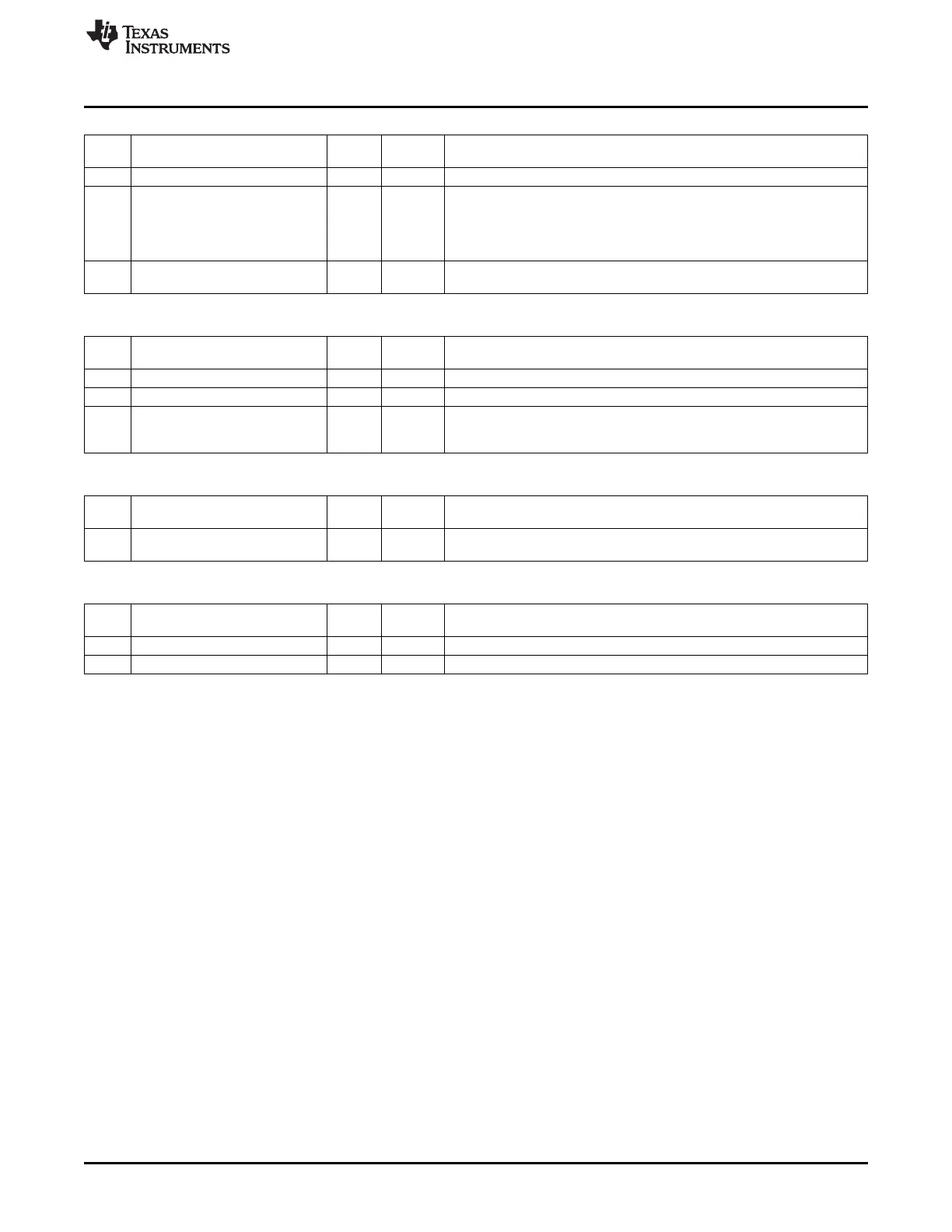

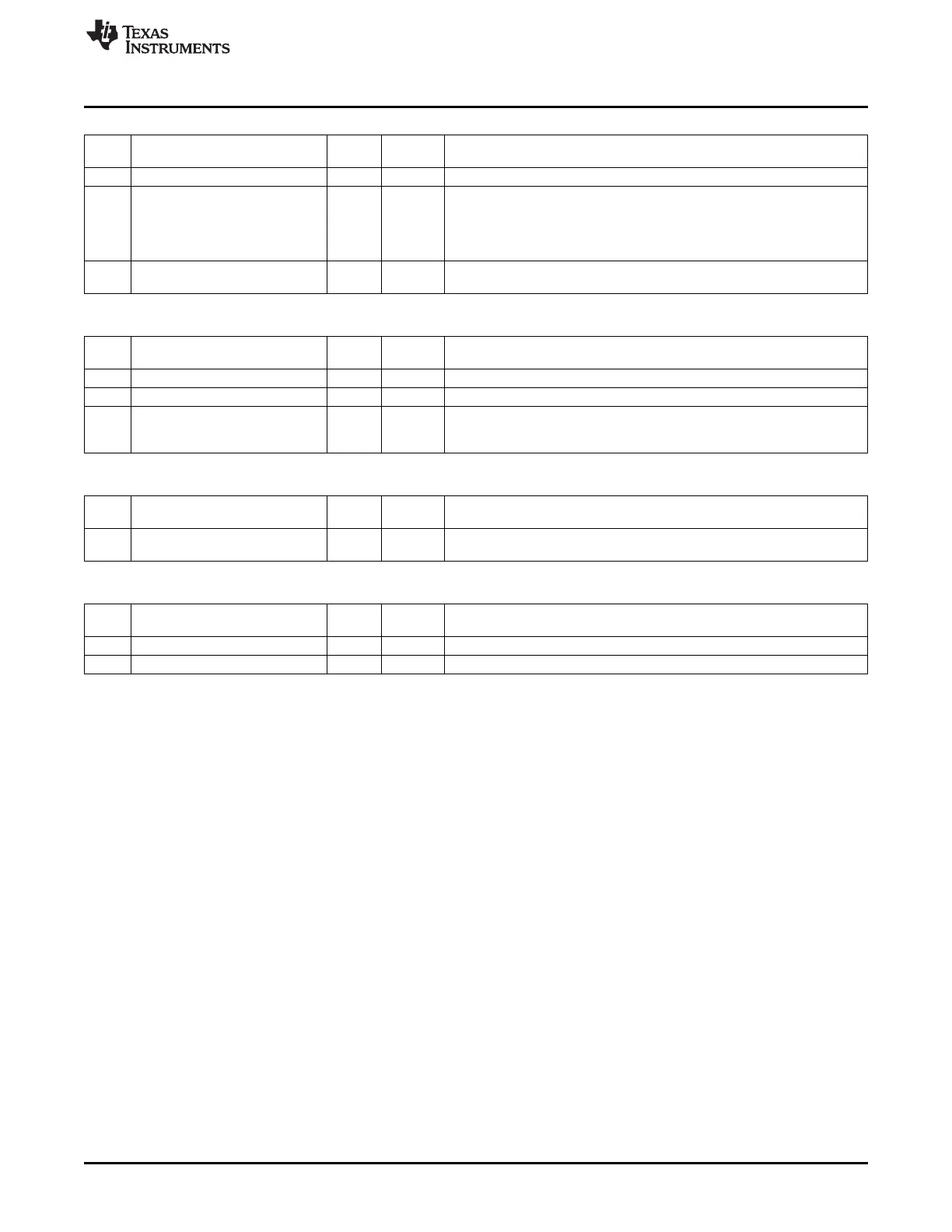

LLECTRL (0x61B1) – LLE Control

Bit

Name Reset R/W Description

No.

7:3 – 0 R0 Reseved. Read as 0

2:1

LLE_MODE_SEL

00 R/W LLE mode. Changing this field has no effect unless LLE_EN is changed

from 0 to 1. The value is reset to 00 when coming up from PM2 or PM3.

00: Proprietary mode (described in this chapter)

01: BLE mode (only for use by the BLE stack)

Others: Reserved

0

LLE_EN

0 R/W 0: LLE held in reset

1: LLE enabled

TXFILTCFG (0x61BC) – TX Filter Configuration

Bit

Name Reset R/W Description

No.

7:4 – 0000 R0 Reserved

3:2 – 11 R/W Reserved

1:0

FC

11 R/W Sets TX anti-aliasing filter to appropriate bandwidth. Reduces spurious

emissions close to signal. For the best value to use, see Table 25-24 and

Table 25-25.

RFRND (0x61BF) – Random Data

Bit

Name Reset R/W Description

No.

7:0

RND

0x00 R Random bits, provided analog part is in random number generation mode

(receiver running without sync)

RFRAMCFG (0x61C0) – Radio RAM Configuration

Bit

Name Reset R/W Description

No.

7:3 – 0000 1 R Reserved

2:0

PRE

000 R/W Selects active memory page for RF core data memory

347

SWRU191C–April 2009–Revised January 2012 CC2541 Proprietary Mode Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...