Registers

www.ti.com

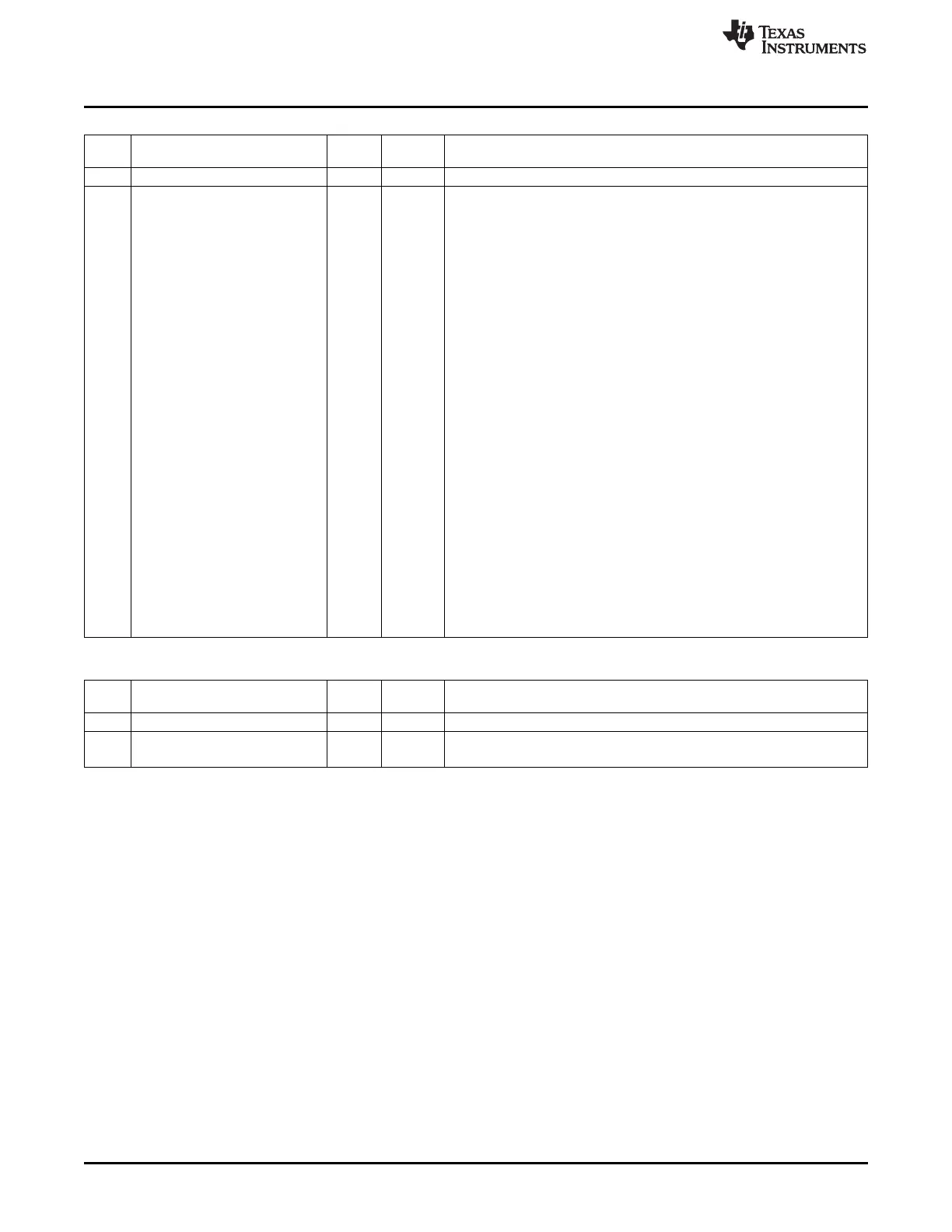

RFFDMA0, (0x61C3) – Radio DMA Trigger 0 Control

Bit

Name Reset R/W Description

No.

7:5 – 000 R Reserved

4:0

DMA0

0x00 R/W Generate a pulse on radio DMA trigger 0 (DMA trigger 19) when:

0x00: Never

0x01: A byte is read from Rx FIFO and more bytes remain or when a byte

arrives in Rx FIFO and it was previously empty.

0x02: A byte is written to Rx FIFO and there is available space left or

when there becomes available space when the Rx FIFO was full.

0x03: Rx FIFO is empty.

0x04: Rx FIFO is full.

0x05: Rx FIFO length equals RFRXFTHRS after a write to Rx FIFO.

0x06: Rx FIFO is read when its size equals RFRXFTHRS.

0x07: Rx FIFO is reset (see Table 25-2).

0x08: Rx FIFO is deallocated (see Table 25-2).

0x09: Rx FIFO is retried (see Table 25-2).

0x0A: Rx FIFO is discarded (see Table 25-2).

0x0B: Rx FIFO is committed (see Table 25-2).

0x0C–0x0F: Reserved (never)

0x10: Never

0x11: A byte is read from Tx FIFO and more bytes remain or when a byte

arrives in Tx FIFO and it was previously empty.

0x12: A byte is written to Tx FIFO and there is available space left or

when there becomes available space when the Tx FIFO was full.

0x13: Tx FIFO is empty.

0x14: Tx FIFO is full.

0x15: Tx FIFO length equals RFTXFTHRS after a write to Tx FIFO.

0x16: Tx FIFO is read when its size equals RFTXFTHRS.

0x17: Tx FIFO is reset (see Table 25-2).

0x18: Tx FIFO is deallocated (see Table 25-2).

0x19: Tx FIFO is retried (see Table 25-2).

0x1A: Tx FIFO is discarded (see Table 25-2).

0x1B: Tx FIFO is committed (see Table 25-2).

0x1C–0x1F: Reserved (never)

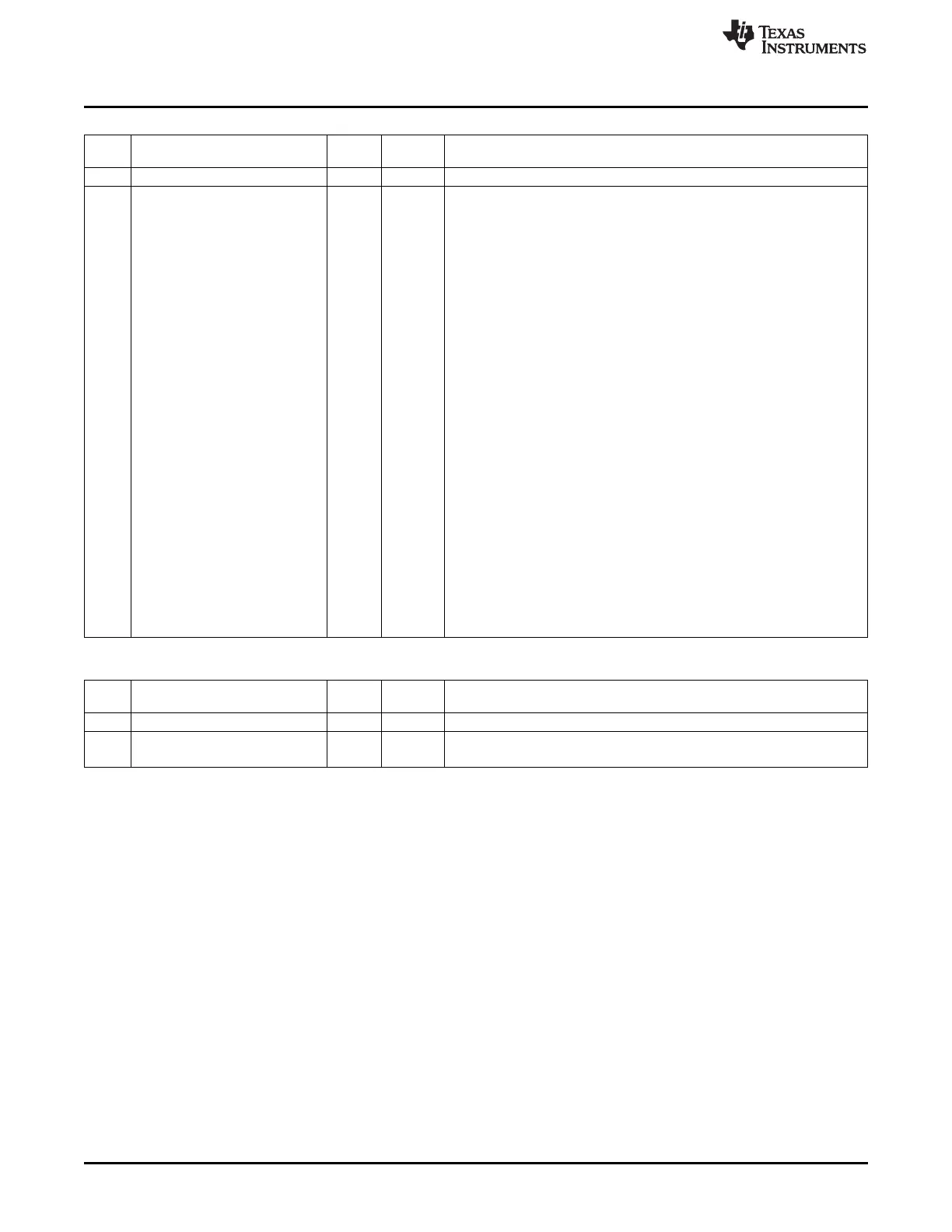

RFFDMA1, (0x61C4) – Radio DMA Trigger 1 Control

Bit

Name Reset R/W Description

No.

7:5 – 0x0 R Reserved

4:0

DMA1

0x0 R/W Condition for generating a pulse on radio DMA trigger 1 (DMA trigger 11).

See RFFDMA0 for the list of conditions.

348

CC2541 Proprietary Mode Radio SWRU191C– April 2009–Revised January 2012

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...