www.ti.com

Registers

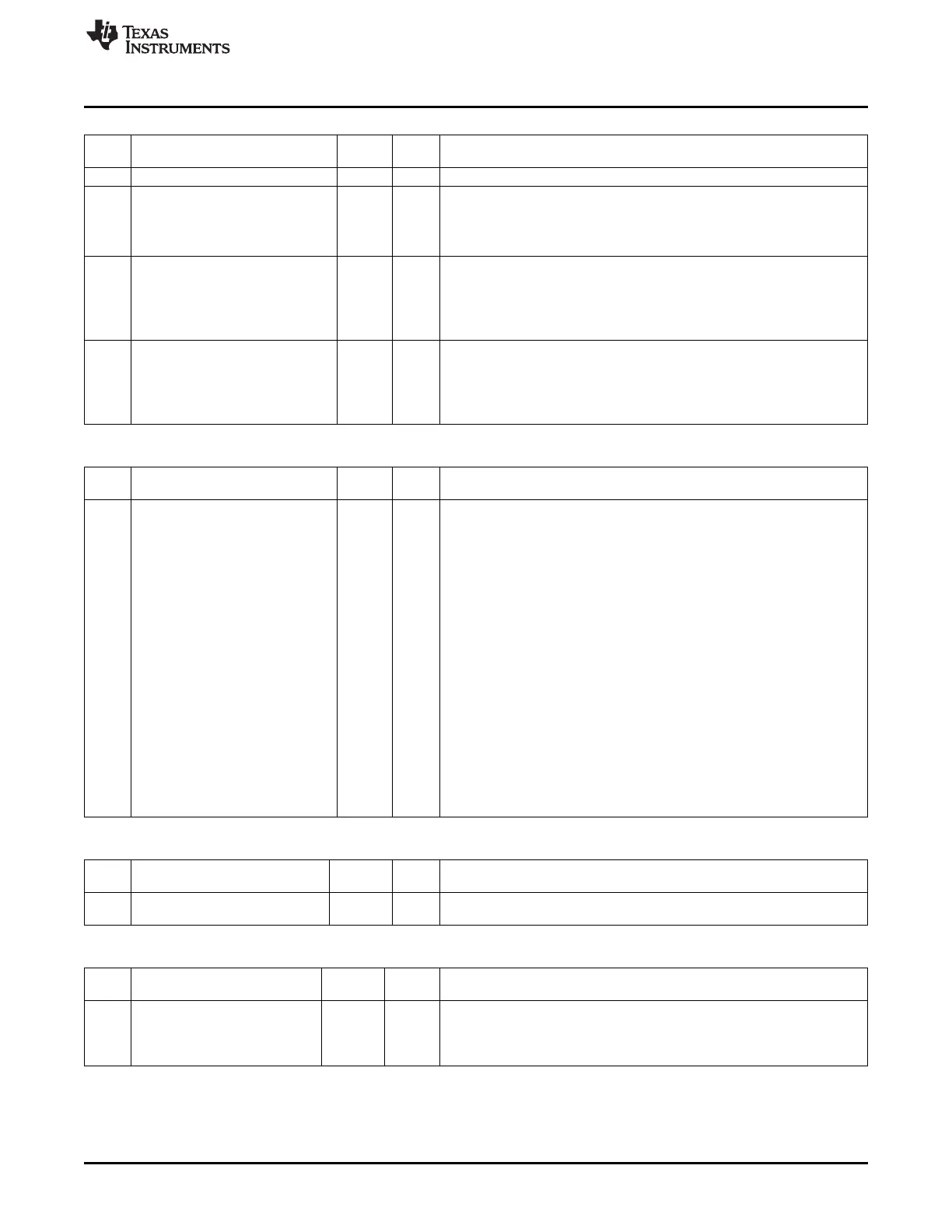

FRMCTRL1 (0x618A) – Frame Handling

Bit Name Reset R/W Description

No.

7:3 – 0000 0 R0 Read as zero

2

PENDING_OR

0 R/W Defines whether the pending data bit in outgoing acknowledgment frames

is always set to 1 or controlled by the main FSM and the address filtering.

0: Pending data bit is controlled by main FSM and address filtering.

1: Pending data bit is always 1.

1

IGNORE_TX_UNDERF

0 R/W Defines whether TX underflow should be ignored or not.

0: Normal TX operation. TX underflow is detected and TX is aborted if

underflow occurs.

1: Ignore TX underflow. Transmit the number of bytes given by the

frame-length field.

0

SET_RXENMASK_ON_TX

1 R/W

Defines whether STXON sets bit 6 in the RXENABLE register or leaves it

unchanged.

0:

Does not affect RXENABLE.

1:

Sets bit 6 in RXENABLE. Used for backwards compatibility with the

CC2420.

RXENABLE (0x618B) – RX Enabling

Bit Name Reset R/W Description

No.

7:0

RXENMASK[7:0]

0x00 R

RXENABLE enables the receiver. A nonzero value in this register causes

the main FSM to enable the receiver when in idle, after transmission, and

after acknowledgement transmission.

The following strobes can modify RXENMASK:

SRXON: Sets bit 7 in RXENMASK

STXON: Sets bit 6 in RXENMASK if SET_RXENMASK_ON_TX = 1

SRFOFF: Clears all bits in RXENMASK

SRXMASKBITSET: Sets bit 5 in RXENMASK

SRXMASKBITCLR: Clears bit 5 in RXENMASK

RXENABLE can be modified directly by the CPU by accessing registers

RXMASKSET and RXMASKCLR.

There might be conflicts between the CSP and CPU operations if both try

to modify RXENMASK simultaneously. To handle the case of simultaneous

access to RXENMASK, the following rules apply:

– If two sources are not in conflict (they modify different parts of the

register), both their requests to modify RXENMASK are processed.

– If both try to modify the mask simultaneously, bus-write operations to

RXMASKSET and RXMASKCLR have priority over the CSP. It is strongly

recommended to avoid this situation.

RXMASKSET (0x618C) – RX Enabling

Bit Name Reset R/W Description

No.

7:0

RXENMASKSET[7:0]

0x00 R0/W

When written, the written data is ORed with RXENMASK and stored in

RXENMASK.

RXMASKCLR (0x618D) – RX Disabling

Bit Name Reset R/W Description

No.

7:0

RXENMASKCLR[7:0]

0x00 R0/W

When written, the written data is inverted and ANDed with RXENMASK and

stored in RXENMASK.

For example, if a 1 is written to one or more bit positions in this register,

the corresponding bits are cleared in RXENMASK.

271

SWRU191C–April 2009–Revised January 2012 CC253x Radio

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Loading...

Loading...