7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 25

UG482 (v1.9) December 19, 2016

Reference Clock Selection and Distribution

Use Modes: Reference Clock Termination

The reference clock input is to be externally AC coupled. Table 2-3 shows the port and attribute

settings required to achieve this.

Reference Clock Selection and Distribution

Functional Description

The GTP transceivers in 7 series FPGAs provide different reference clock input options. Clock

selection and availability differs slightly from 7 series GTX/GTH transceivers in that reference

clock routing is east and west bound rather than north and south bound.

Architecturally, the concept of a Quad (or Q), contains a grouping of four GTPE2_CHANNEL

primitives, one GTPE2_COMMON primitive, two dedicated external reference clock pin pairs, and

dedicated reference clock routing. The GTPE2_COMMON primitive must always be instantiated,

and the GTPE2_CHANNEL primitive must be instantiated for each transceiver. For the largest

Artix™-7 device (XC7A200T-FFG1156), the reference clock supplied to the PLLs in a given Quad

can also be sourced from the adjacent Quad in the same half of the device. A Quad located in the top

half of the device can share its two local reference clocks with the other Quad located in the top half.

Similarly, a Quad located in the bottom half of the device can share its two reference clocks with the

other Quad located in the bottom half.

Reference clock features include:

• Clock routing for east and west bound clocks.

• Flexible reference clock inputs available for PLL0 and PLL1.

• Static or dynamic selection of the reference clock for PLL0 and PLL1.

Figure 2-2 shows the reference clock architecture with the GTPE2_COMMON primitive, two

dedicated reference clock pin pairs, and dedicated east or west reference clock routing. Each

GTPE2_COMMON in a Quad has four clock inputs available:

• Two local reference clock pin pairs, GTREFCLK0 or GTREFCLK1

• Two reference clock pin pairs from the other Quad situated in the same half of the device

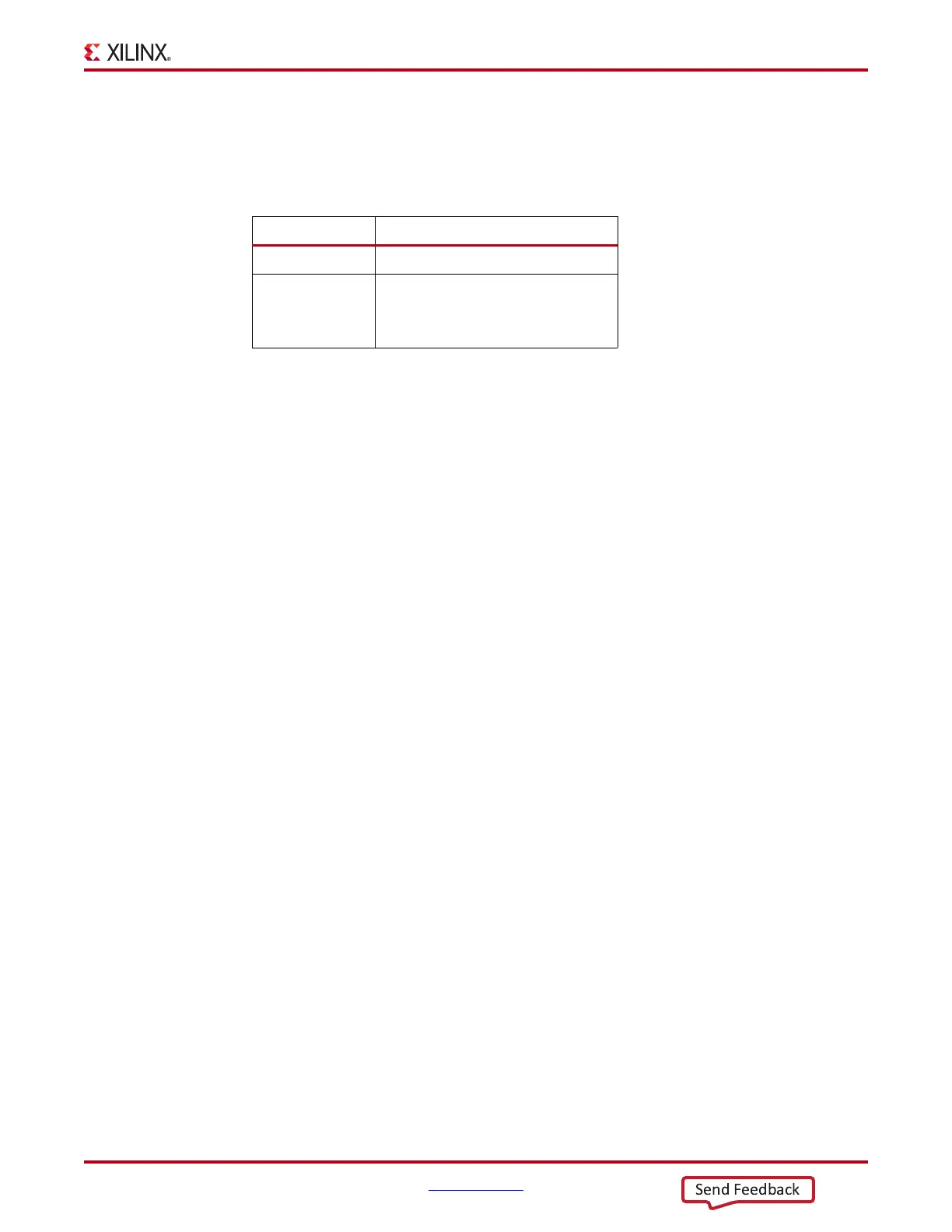

Table 2-3: Port and Attribute Settings

Input Type Settings

Ports CEB = 0

Attributes

CLKRCV_TRST = TRUE

CLKCM_CFG = TRUE

CLKSWING_CFG = 2'b11

Loading...

Loading...