196 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

Setting Clock Correction Sequences

The clock correction sequences are programmed using the CLK_COR_SEQ_1_* attributes and

CLK_COR_SEQ_LEN. Each CLK_COR_SEQ_1_* attribute corresponds to one subsequence in

clock correction sequence 1. CLK_COR_SEQ_LEN is used to set the number of subsequences to be

matched. If the 40-bit or 20-bit internal datapaths are used, the clock correction circuit matches all

10 bits of each subsequence. If the 16-bit or 32-bit internal datapaths are used, only the right-most

eight bits of each subsequence are used.

A second, alternate clock correction sequence can be activated by setting CLK_COR_SEQ_2_USE

to TRUE. The first and second sequences share length settings, but use different subsequence values

for matching. Set the CLK_COR_SEQ_2_* attributes to define the subsequence values for the

second sequence.

When using 8B/10B decoding (RX8B10BEN is High), CBCC_DATA_SOURCE_SEL is set to

DECODED to search the output of the 8B/10B decoder for sequence matches instead of

non-decoded data. This allows the circuit to look for 8-bit values with either positive or negative

disparity, and to distinguish K characters from regular characters (see TX 8B/10B Encoder, page 83

and RX 8B/10B Decoder, page 170 for details). Figure 4-45 shows how to set a clock correction

sequence byte when RX8B10BEN is High and CBCC_DATA_SOURCE_SEL is set to DECODED.

When CBCC_DATA_SOURCE_SEL is set to ENCODED, the sequence must exactly match

incoming raw data. When RX_DISPERR_SEQ_MATCH is set to FALSE,

CLK_COR_SEQ_x_y[9] is not used for matching.

Some protocols use clock correction sequences with don’t care subsequences. The clock correction

circuit can be programmed to recognize these sequences using CLK_COR_SEQ_1_ENABLE and

CLK_COR_SEQ_2_ENABLE. When the enable bit for a sequence is Low, that byte is considered

matched no matter what the value is. Figure 4-46 shows the mapping between the clock correction

sequences and the clock correction sequence enable bits.

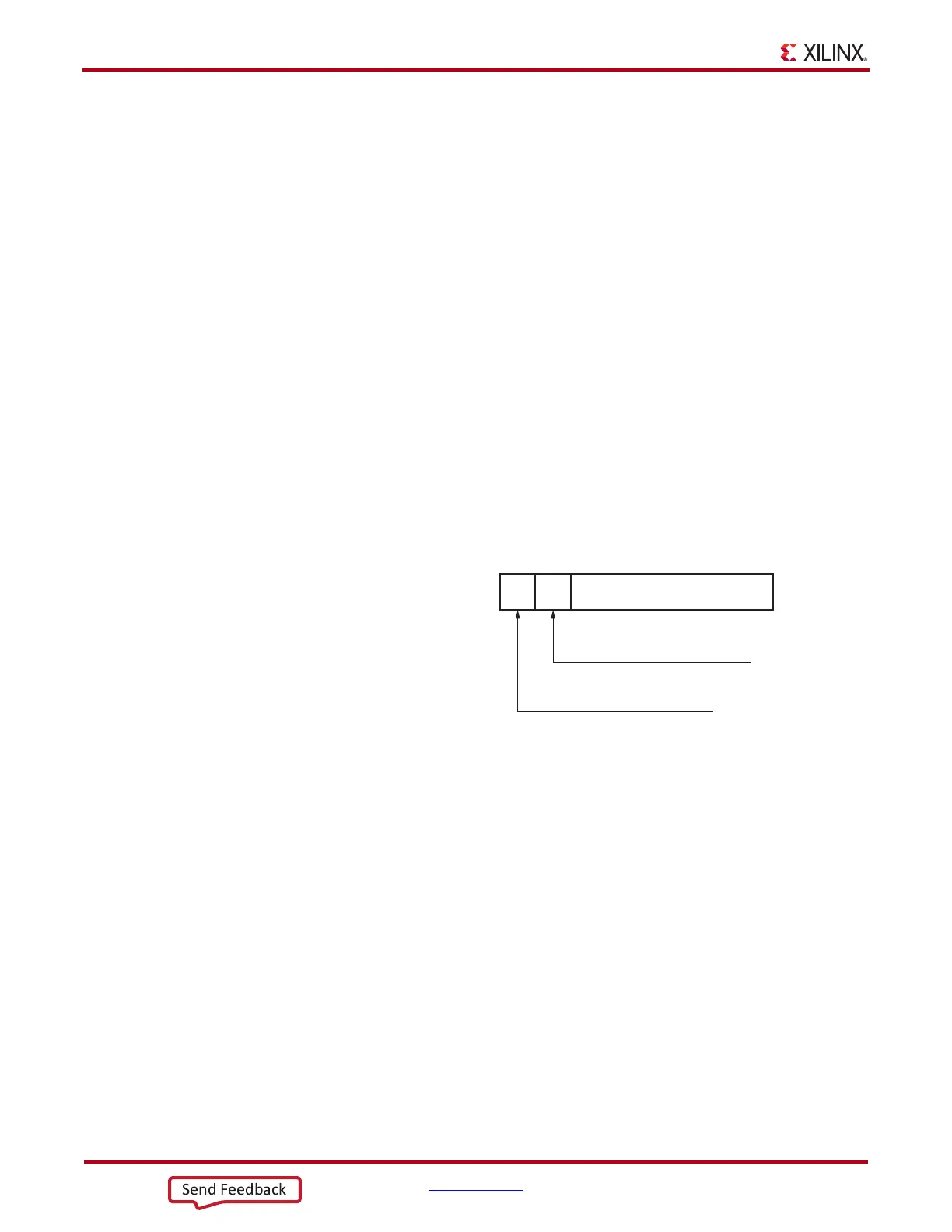

X-Ref Target - Figure 4-45

Figure 4-45: Clock Correction Subsequence Settings with

CBCC_DATA_SOURCE_SEL = DECODED

UG482_c4_27_111011

CLK_COR_SEQ_x_y 9 8 7:0

8-bit Clock Correction Sequence

1 = Sequence is a K Character

0 = Sequence is a Regular Character

1 =

Sequence Uses Inverted Disparity

0 =

Sequence Uses Regular Disparity

Loading...

Loading...