162 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

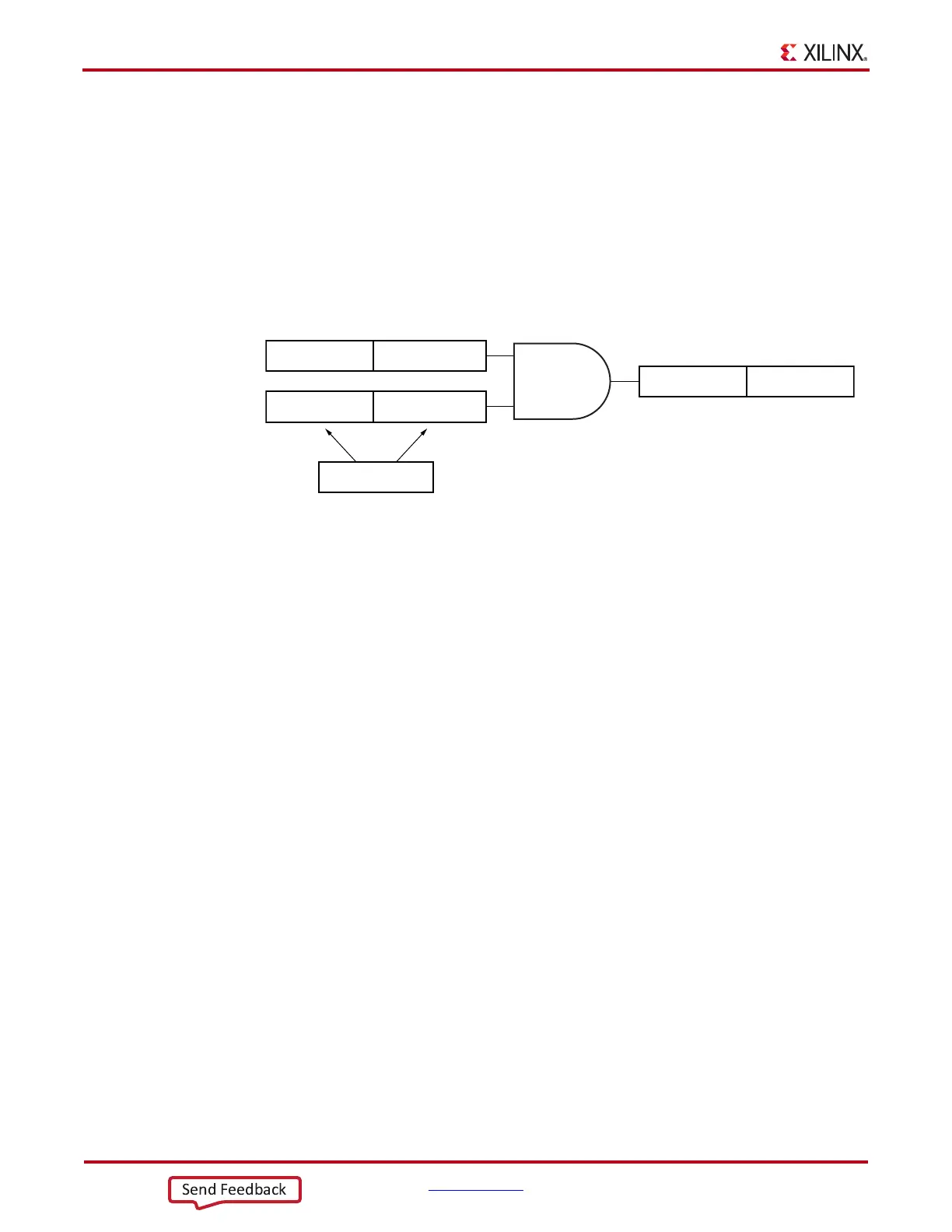

Figure 4-29 shows how a comma is combined with ALIGN_COMMA_ENABLE to make a

wild-carded comma for a 20-bit internal comma. If ALIGN_COMMA_DOUBLE is TRUE, the

MCOMMA and PCOMMA patterns are combined so that the block searches for two commas in a

row. The number of bits in the comma depends on RX_DATA_WIDTH. Either a 16-bit or a 20-bit

comma alignment mode is possible. A double comma is only detected when the received data has a

PCOMMA defined by ALIGN_PCOMMA_VALUE followed by an MCOMMA defined by

ALIGN_MCOMMA_VALUE with no extra bits in between.

Activating Comma Alignment

Commas are aligned to the closest boundary providing they are found while comma alignment is

active. RXMCOMMAALIGNEN is driven High to align on the MCOMMA pattern.

RXPCOMMAALIGNEN is driven High to activate alignment on the PCOMMA pattern. Both

enable ports are driven to align to either pattern. When ALIGN_COMMA_DOUBLE is TRUE, both

enable ports must always be driven to the same value.

Alignment Status Signals

While MCOMMA or PCOMMA alignment is active, any matching comma pattern causes the block

to realign to the closest boundary. After successful alignment, the block holds

RXBYTEISALIGNED High. At this time, RXMCOMMAALIGNEN and

RXPCOMMAALIGNEN can be driven Low to turn off alignment and keep the current alignment

position. RXPCOMMAALIGNEN must be TRUE for PCOMMAs to cause RXBYTEISALIGNED

to go High. Similarly, RXMCOMMAALIGNEN must be TRUE for MCOMMAs to cause

RXBYTEISALIGNED to go High. Commas can arrive while RXBYTEISALIGNED is High. If the

commas arrive aligned to boundaries, there is no change. If the commas arrive out of position, the

block deasserts RXBYTEISALIGNED until the commas are aligned again. If alignment is still

activated for the comma that arrives, the block automatically aligns the new comma to the closest

boundary and drives RXBYTEREALIGN High for one RXUSRCLK2 cycle.

In applications that operate at a line rate greater than 5 Gb/s and have excessive noise in the system,

the byte align block might falsely align to a wrong byte boundary and falsely assert the

RXBYTEISALIGNED signal when no valid data is present. In such applications, a system level

check should be in place for checking the validity of the RXBYTEISALIGNED indicator and data.

In systems that use the OOB (RX Out-of-Band signaling) block e.g., PCIe, SATA, after locking to a

valid byte boundary and asserting the RXBYTEISALIGNED signal, the byte align block might

occasionally de-assert the RXBYTEISALIGNED signal even when there is no change in the byte

X-Ref Target - Figure 4-29

Figure 4-29: Extended Comma Pattern Masking

0010100010

xx10100001

0011111111

0010100001

0011111111

xx10100010

0011111111

ALIGN_MCOMMA_VALUE

and

ALIGN_PCOMMA_VALUE

(ALIGN_COMMA_DOUBLE = TRUE)

Pattern Required for

Comma Detection

(x = don’t care)

ALIGN_COMMA_ENABLE

UG482_c4_18_111011

Loading...

Loading...