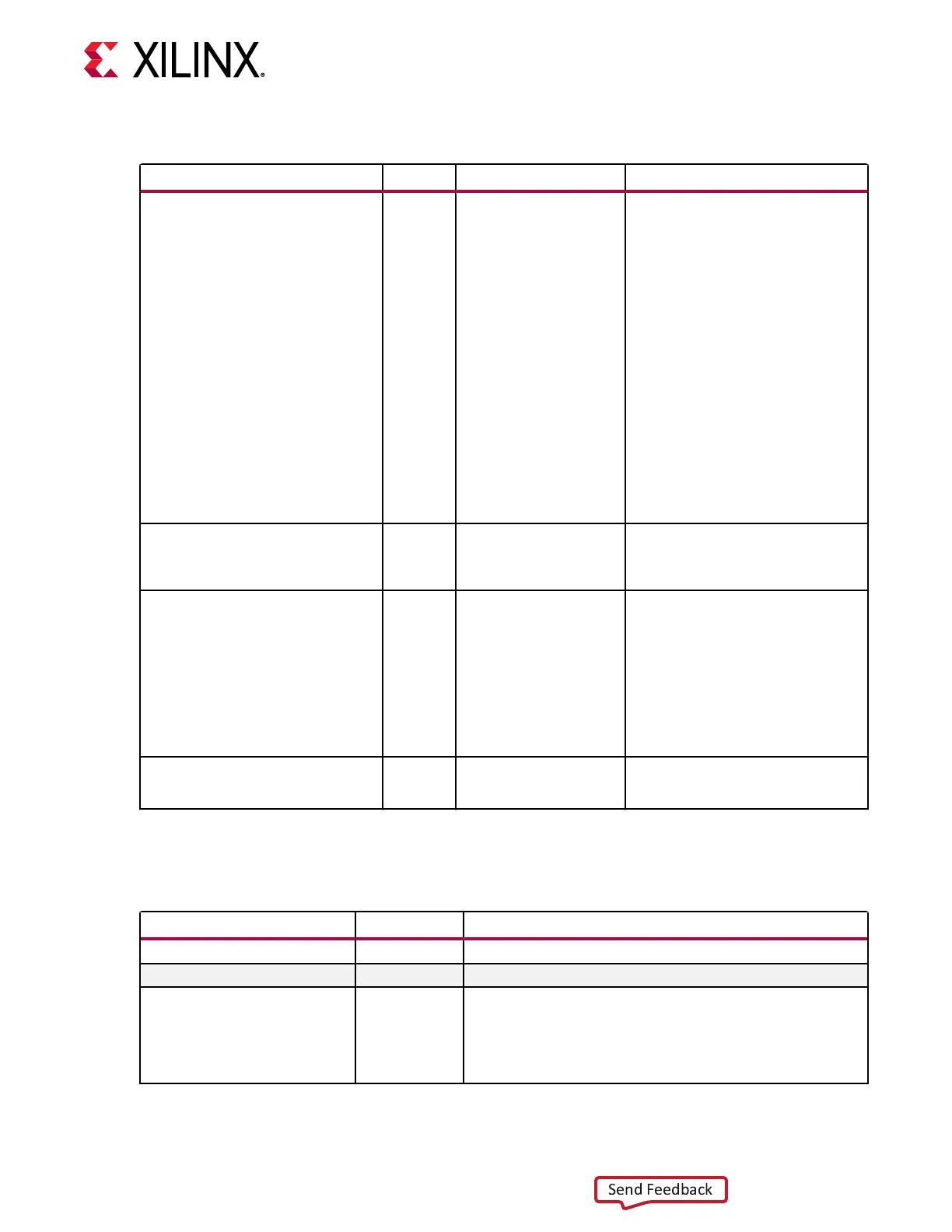

Table 60: Pattern Checker Ports (cont'd)

Port Dir Clock Domain Description

CH[0/1]_RXPRBSPTN[3:0] In CH0_TXUSRCLK2 Receiver PRBS checker test pattern

control. Only these settings are valid:

4’b0000: Standard operation

mode (PRBS check is off)

4’b0001: PRBS-7

4’b0010: PRBS-9

4’b0011: PRBS-15

4’b0100: PRBS-23

4’b0101: PRBS-31

4’b0110: PRBS-13

After changing patterns, perform a

reset of the RX or a reset of the PRBS

error counter

(CH[0/1]_RXPRBSCSCNTRST) such that

the RX pattern checker can attempt to

reestablish the link acquired. No

checking is done for non-PRBS

patterns.

CH[0/1]_RXPRBSERR Out CH[0/1]_RXUSRCLK2 This non-sticky status output indicates

that PRBS errors have occurred. Only

use CH[0/1]_RX_PRBSERR to read the

precise bit error counts.

CH[0/1]_RXPRBSLOCKED Out CH[0/1]_RXUSRCLK2 Output to indicate that the RX PRBS

checker has been error free for

CH[0/1]_RX_PCS_CFG1[12:5] cycles after

reset. After being asserted High,

CH[0/1]_RXPRBSLOCKED does not

deassert until reset of the RX pattern

checker via a reset of the RX

(GTRXRESET, RXPMARESET, or

RXPCSRESET in sequential mode) or a

reset of the PRBS error counter

(CH[0/1]_RXPRBSCSCNTRST).

CH[0/1]_RXPRBSCNTSTOP

In CH[0/1]_RXUSRCLK2 Input control to stop the error counter.

The PRBS checker needs to restart the

error counter after a PRBS stop.

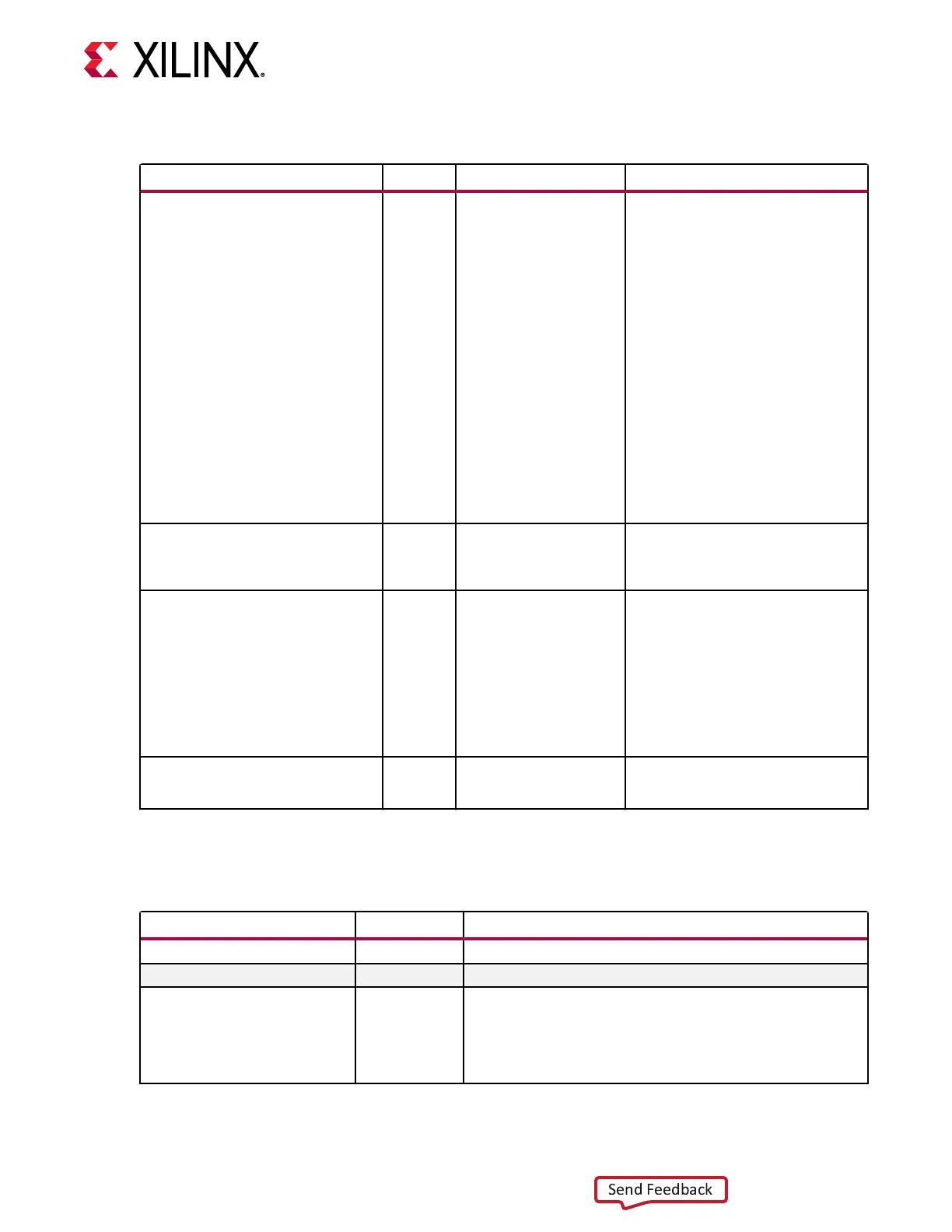

The following table denes the paern checker aributes.

Table 61: Pattern Checker Attributes

Attribute Type Description

CH[0/1]_TX_PCS_CFG1 16-bit Reserved.

Bit Name Address Description

RXPRBSERR_LOOPBACK [7] When this attribute is set to 1, the CH[0/1]_RXPRBSERR bit is

internally looped back to CH[0/1]_TXPRBSINERR of the same GTM

transceiver. This allows synchronous and asynchronous jitter

tolerance testing without worrying about data clock domain

crossing. When this attribute is set to 1b’0, CH[0/1]_TXPRBSINERR

is forced onto the TX PRBS.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 102

Loading...

Loading...