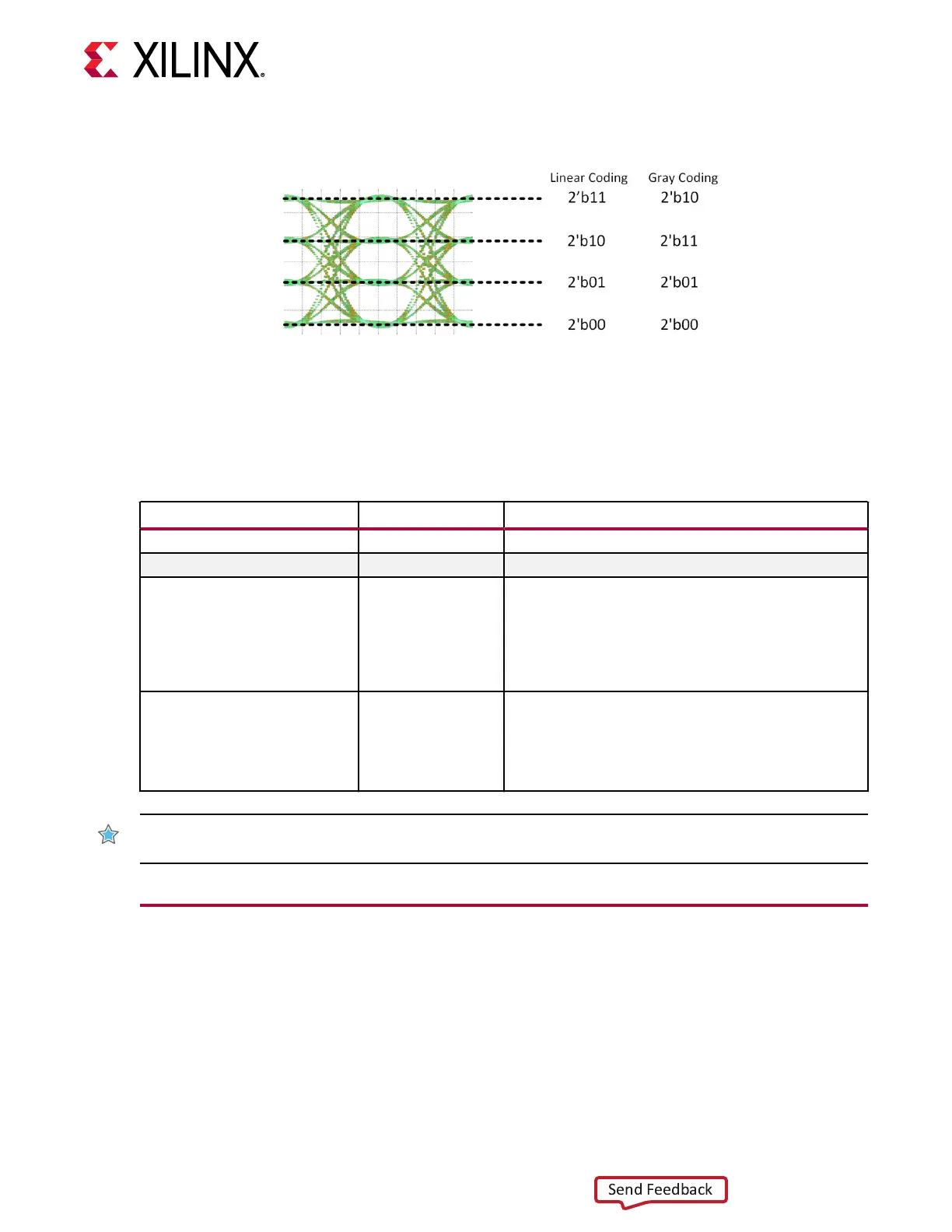

Figure 33: Transmitted PAM4 Signal Bit Encoding

Ports and Attributes

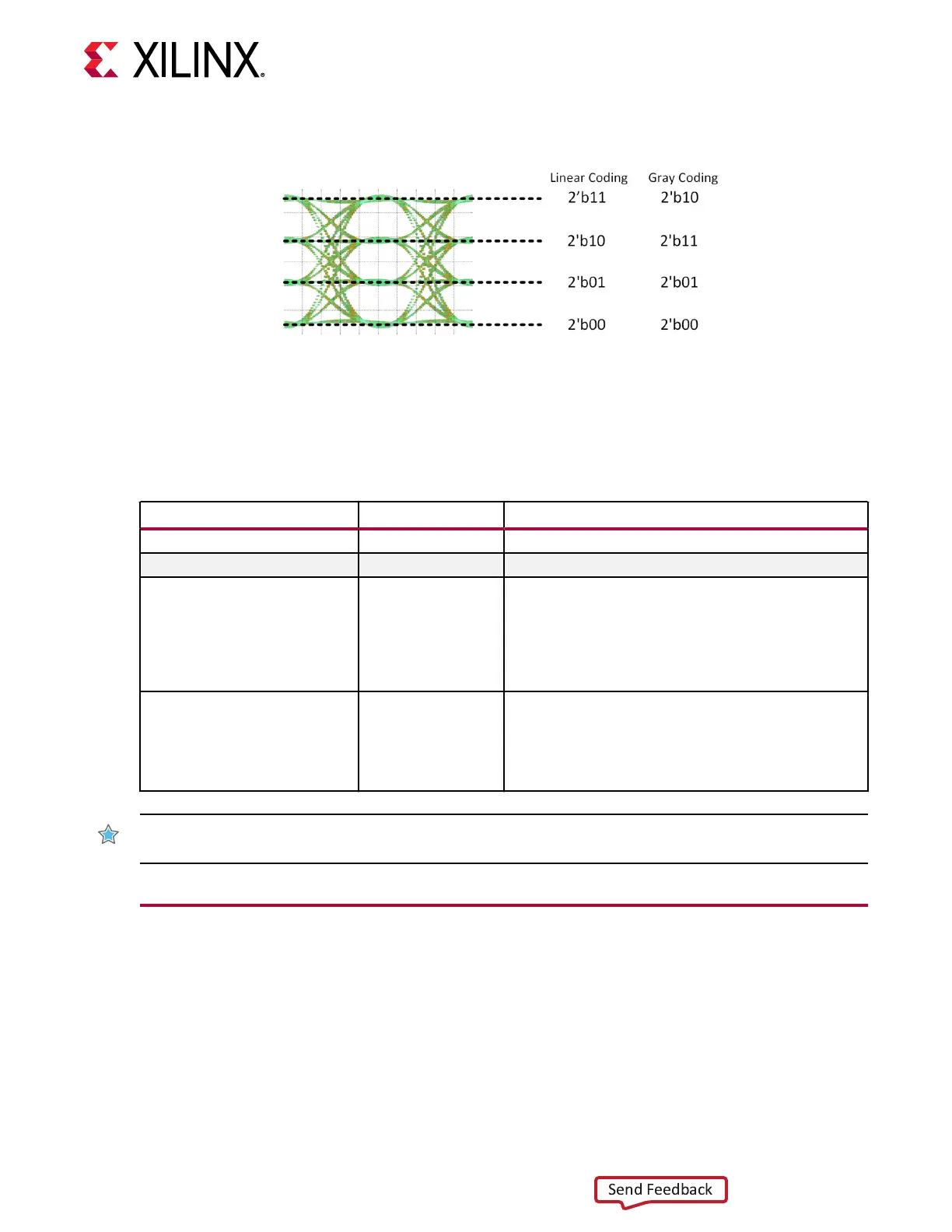

The following table denes the aributes required for TX Gray encoder control.

Table 41: Gray Encoder Attributes

Attribute Type Description

CH[0/1]_TX_PCS_CFG0 16-bit Reserved.

Bit Name Address Description

TX_GRAY_ENDIAN [13] In PAM4 mode, this attribute controls transmitted

endianness. In NRZ mode, the default Wizard value must be

used.

1’b0: Non-inverting.

1’b1: Inverting.

TX_GRAY_BYP_EN

[12] In PAM4 mode, this attribute enables Gray encoding. In NRZ

mode, the default Wizard value must be used.

1’b0: Enables Gray encoding.

1’b1: Disables Gray encoding.

IMPORTANT! In PAM4 mode, if Gray encoder is enabled for the transmier, the receiver Gray decoder

should also be enabled for proper data recovery.

TX Pre-Coder

GTM transmiers in UltraScale+ devices support pre-coding. Pre-coding can be used to reduce

receiver decision feedback equalizaon (DFE) error propagaon by reducing 1-tap burst error

runs into two errors for every error event.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 72

Loading...

Loading...