Implementation

It is a common pracce to dene the locaon of GTM transceiver Duals early in the design

process to ensure correct usage of clock resources and to facilitate signal integrity analysis during

board design. The implementaon ow facilitates this pracce through the use of locaon

constraints in the XDC le.

The posion of each GTM transceiver Dual primive is specied by an XY coordinate system that

describes the column number and the relave posion within that column. For a given device/

package combinaon, the transceiver with the coordinates X0Y0 is located at the lowest posion

of the lowest available bank.

There are two ways to create an XDC le for designs that ulize the GTM transceivers. The

preferred method is to use the UltraScale+ FPGAs GTM Transceivers Wizard. The Wizard

automacally generates XDC le templates that congure the transceivers and contain

placeholders for GTM transceiver placement informaon. The XDC les generated by the Wizard

can then be edited to customize operang parameters and placement informaon for the

applicaon.

The second approach is to create the XDC le manually. When using this approach, you must

enter both conguraon aributes that control transceiver operaon as well as the locaon

parameters. Care must be taken to ensure that all of the parameters needed to congure the

GTM transceiver are correctly entered. A GTM_DUAL primive must be instanated as shown in

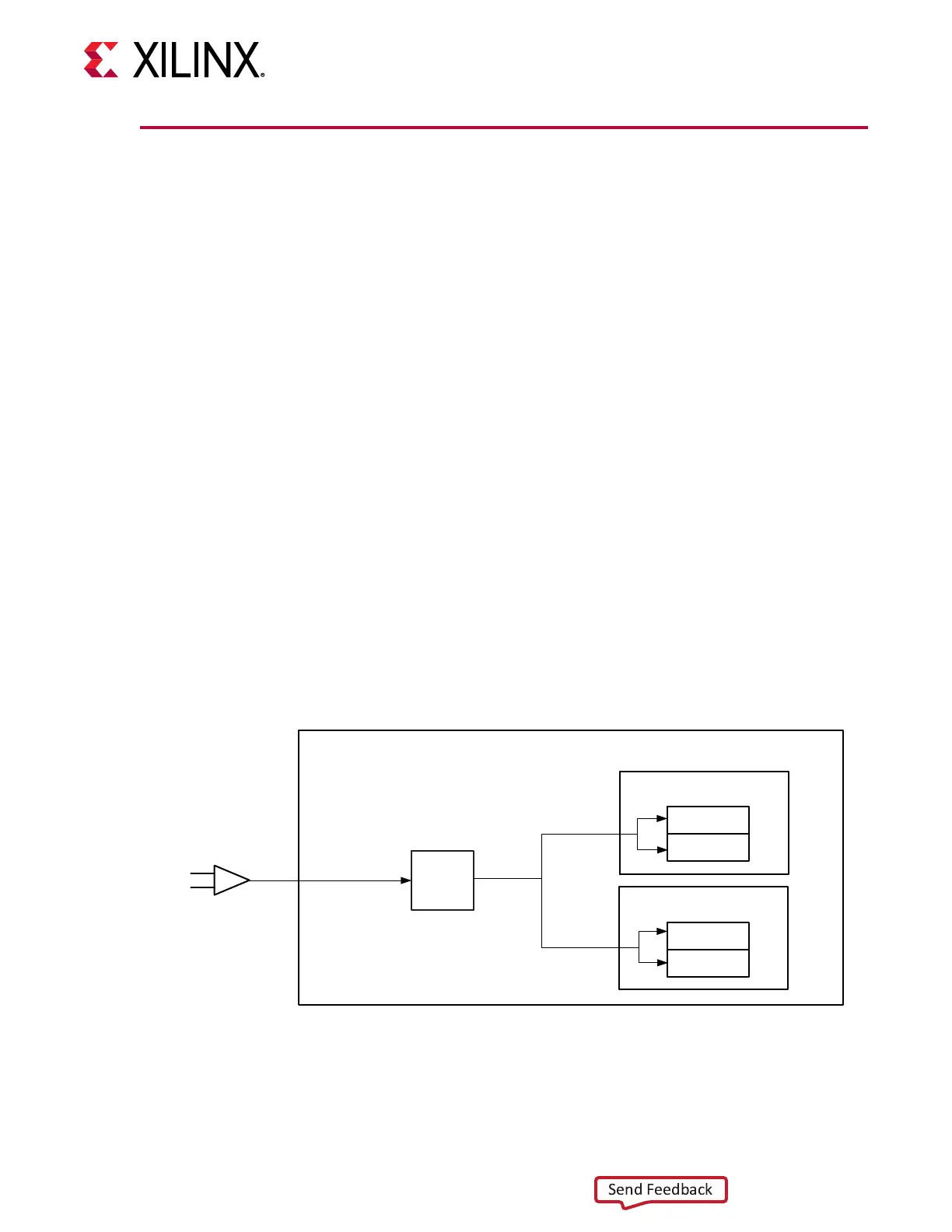

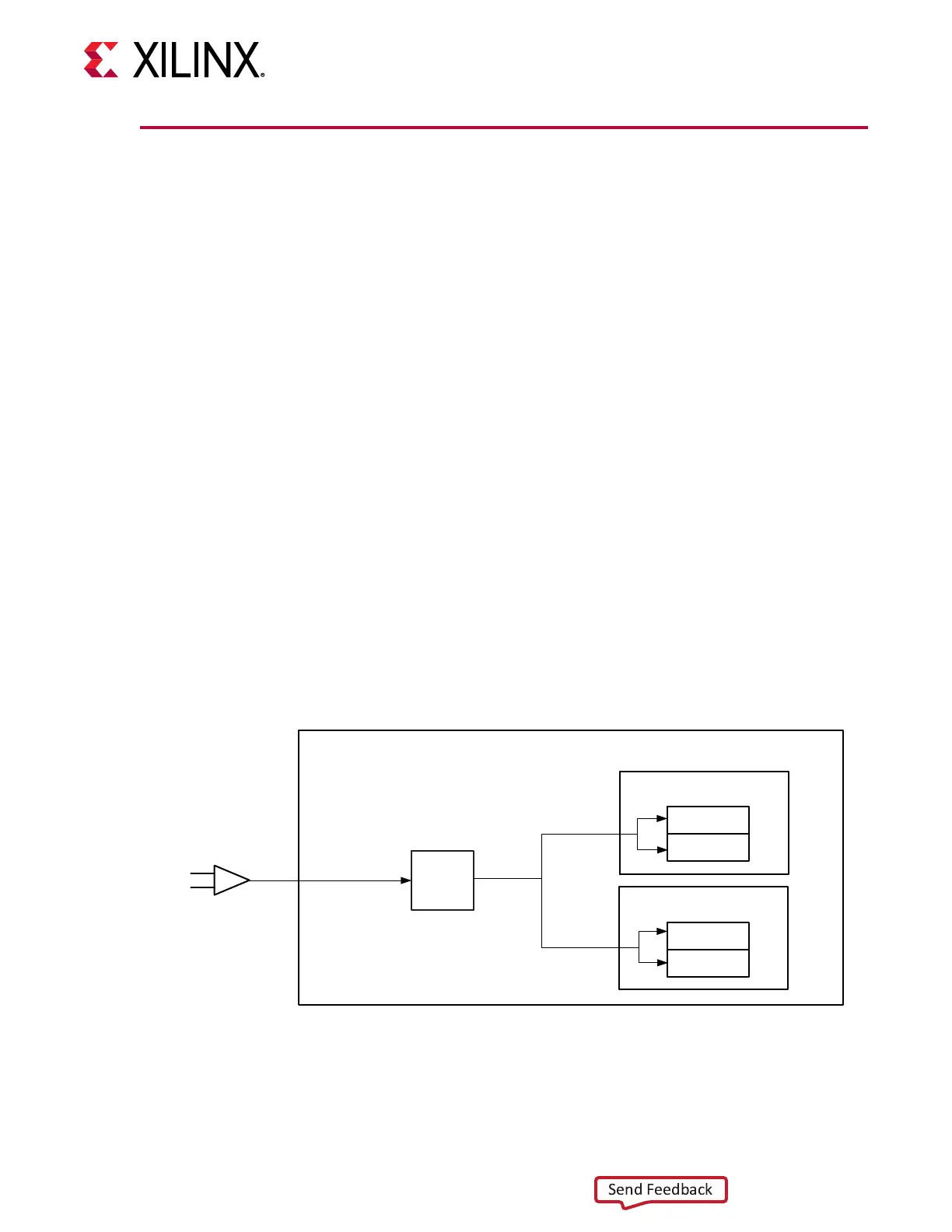

the following gure.

Figure 3: One-Dual, Two-Channel Configuration (Reference Clock from the LCPLL)

LCPLL

GTM_DUAL

GTM Channel 0 (CH0)

RX

TX

GTM Channel 1 (CH1)

RX

TX

IBUFDS_GTM

X20212-061418

Each dual contains an LCPLL. Therefore, a reference clock can be connected directly to a

GTM_DUAL primive.

Chapter 1: Transceiver and Tool Overview

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 11

Loading...

Loading...