Table 56: RX Fabric Clock Output Control Ports

Port Dir Clock Domain Description

CH[0/1]_RXOUTCLKSEL[2:0] In Async This port must be set to 3'b000.

CH[0/1]_RXOUTCLK Out Clock Reserved.

CH[0/1]_RXPROGDIVCLK Out Clock RXPROGDIVCLK is the parallel output clock from

the RX programmable divider. This clock is the

recommended output to the interconnect logic

through BUFG_GT.

RXRECCLK[0/1] Out Clock RXRECCLK is the same as RXPROGDIVCLK, and it

can be routed to the MGTREFCLK output pad.

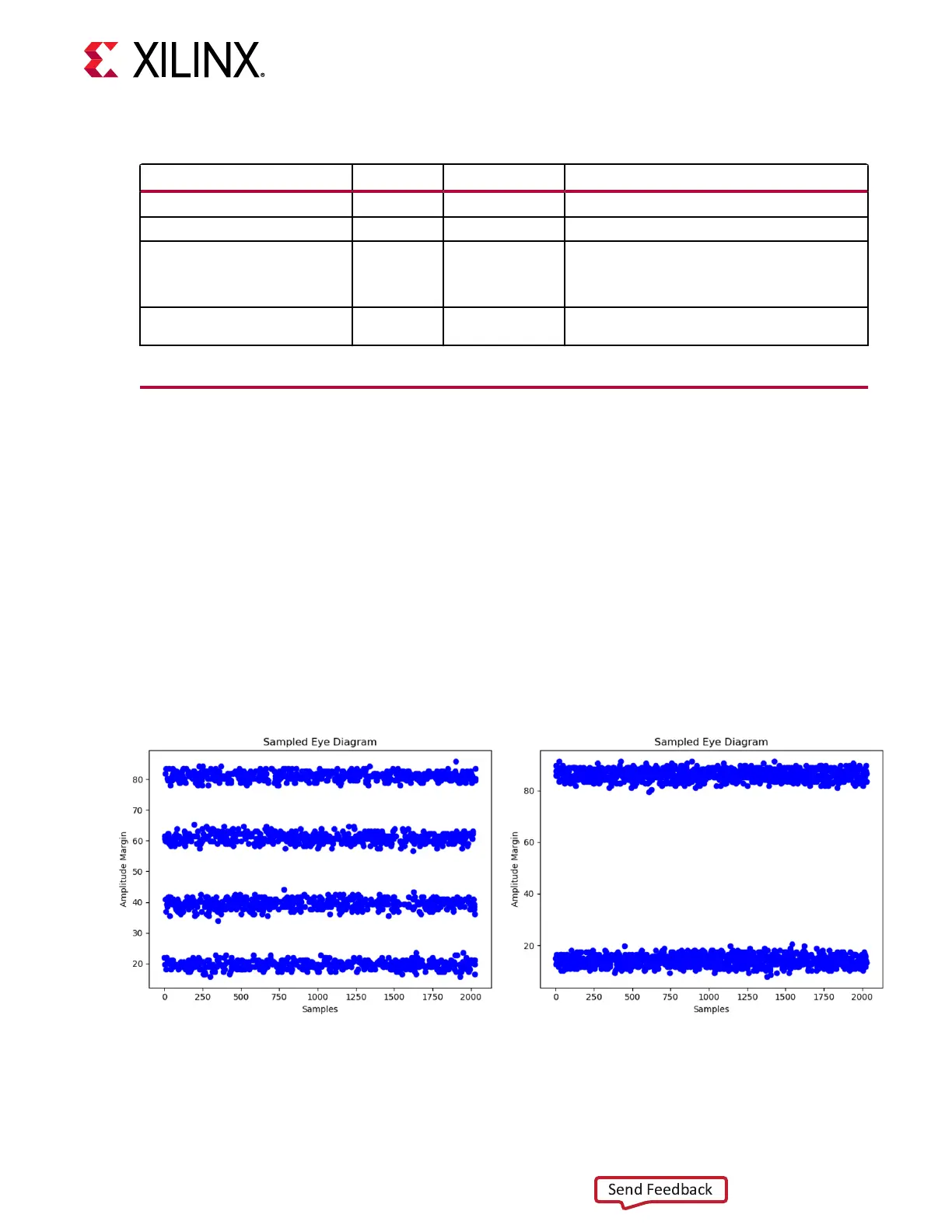

RX Margin Analysis

As line rates and channel aenuaon increase, the receiver equalizers are more oen enabled to

overcome channel aenuaon. This poses a challenge to system bring-up because the quality of

the link cannot be determined by measuring the far-end eye opening at the receiver pins. At high

line rates, the received eye measurement on the printed circuit board can appear to be

completely closed even though the internal eye aer the receiver equalizer is open.

Because the GTM receiver is ADC-based, the convenonal eye scan used in the previous family

of transceivers (such as GTH and GTY transceivers) is not possible. The GTM RX provides a

sampled eye diagram that can be used to measure and visualize the receiver signal margin aer

the equalizer, as shown in the following gure.

Figure 42: Sampled Eye Diagram for (a) PAM4 and (b) NRZ Modulation

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 98

Loading...

Loading...