Table 59: RX Polarity Control Ports

Port Dir Clock Domain Description

CH[0/1]_RXPOLARITY

1

In CH[0/1]_RXUSRCLK2 The CH[0/1]_RXPOLARITY port can invert

the polarity of incoming data:

0: Not inverted. RXP is positive, and

RXN is negative.

1: Inverted. RXP is negative, and RXN

is positive.

Notes:

1. CH[0/1]_RXPOLARITY can be tied High if the polarity of RXP and RXN needs to be reversed.

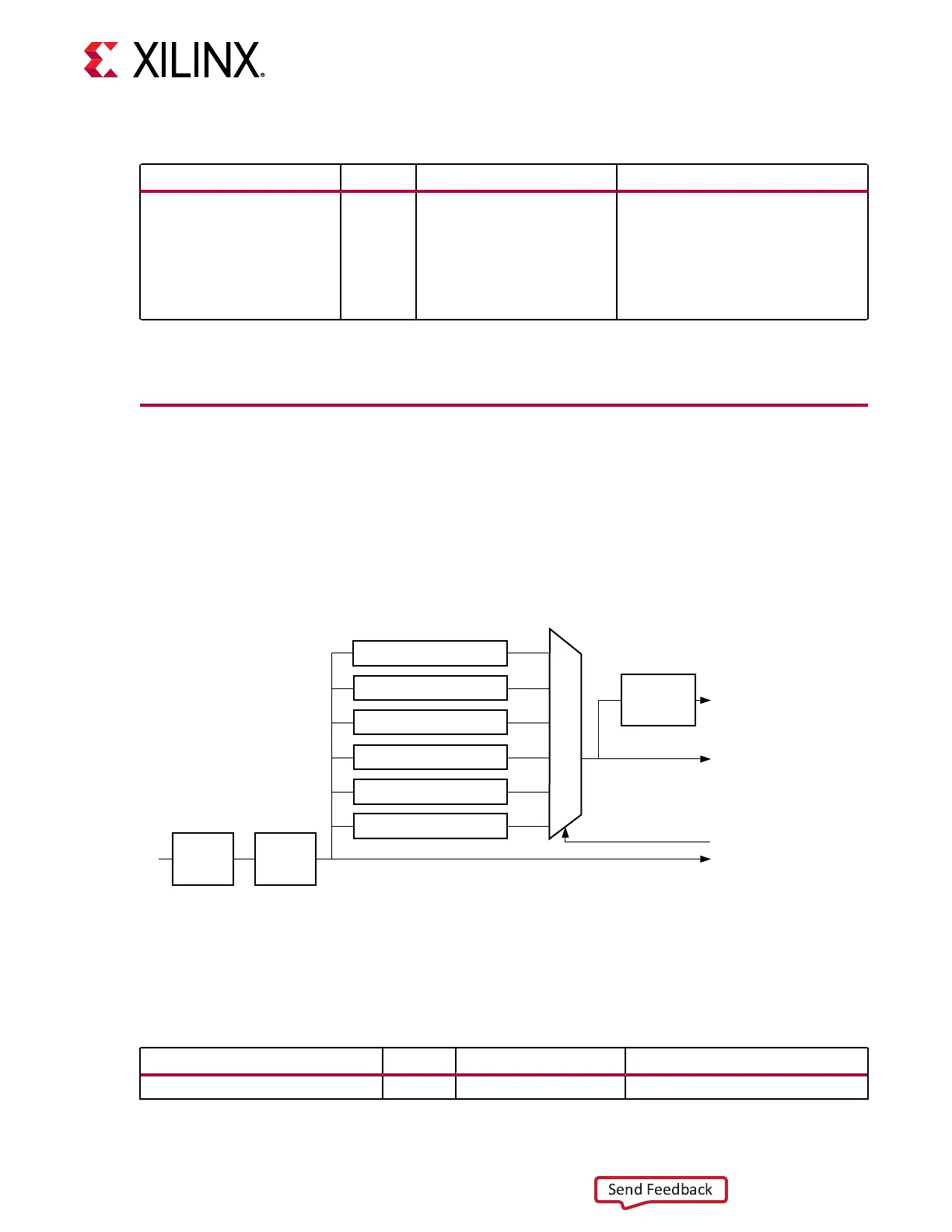

RX Pattern Checker

The GTM receiver includes a built-in PRBS checker (see the following gure). This checker can be

set to check for one of the six industry-standard PRBS paerns. The checker is self-synchronizing

and works on the incoming data before comma alignment or decoding. This funcon can be used

to test the signal integrity of the channel.

Figure 43: RX Pattern Checker Block

Polarity

Control

SIPO

Error

Counter

(32 bits)

PRBS-31 Pattern Checker

PRBS-23 Pattern Checker

PRBS-15 Pattern Checker

PRBS-9 Pattern Checker

RX_PRBS_ERR_CNT

CH[0/1]RXPRBSERR

CH[0/1]RXDATA

CH[0/1]RXPRBSPTN

PRBS-13 Pattern Checker

PRBS-7 Pattern Checker

Error

X20928-053118

Ports and Attributes

The following table denes the paern checker ports.

Table 60:

Pattern Checker Ports

Port Dir Clock Domain Description

CH[0/1]_RXPRBSCSCNTRST In CH[0/1]_RXUSRCLK2 Reset the PRBS error counter.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 101

Loading...

Loading...