11. RX FEC

RX Analog Front End

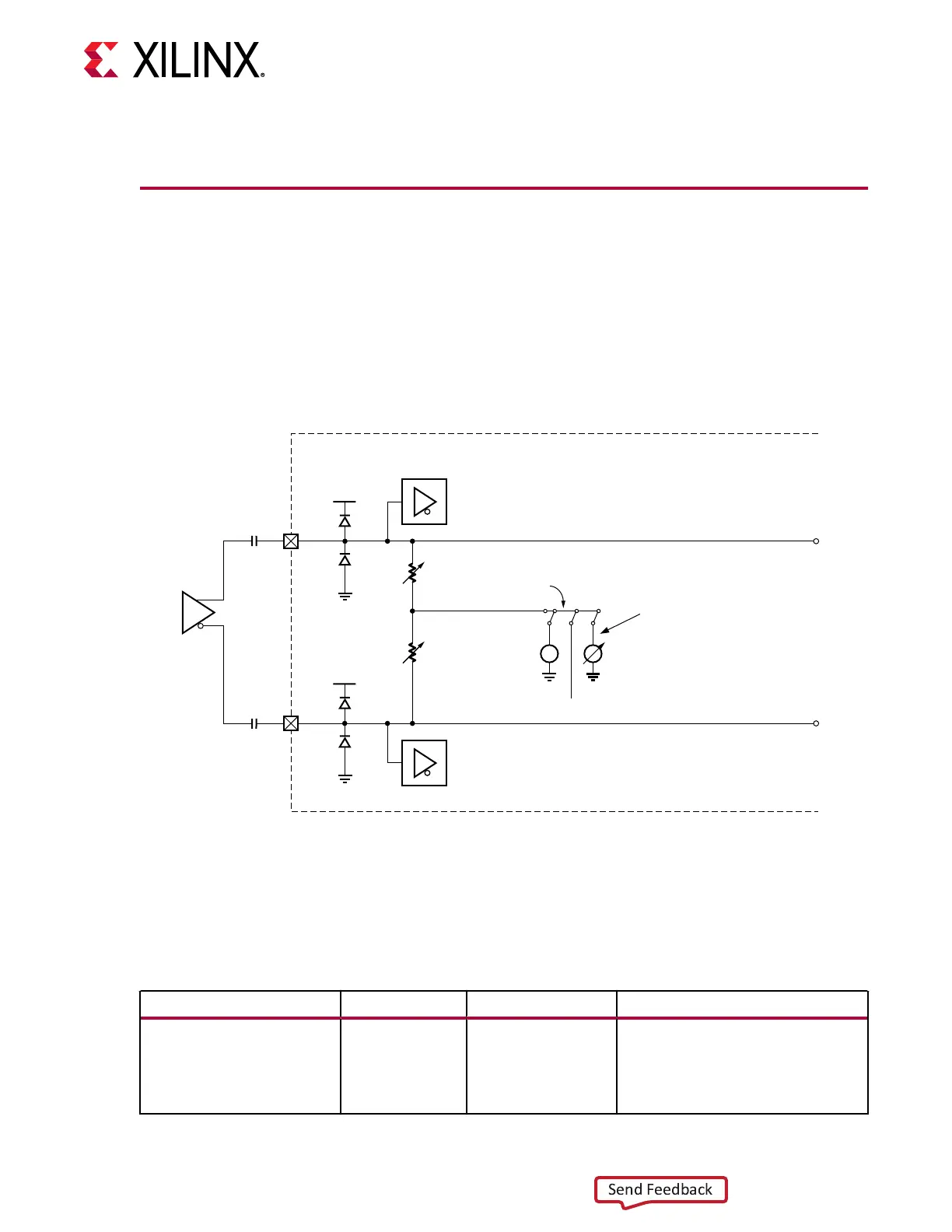

The RX analog front end (AFE) is an ADC-based input dierenal buer. It has the following

features:

• Congurable RX terminaon voltage

• Calibrated terminaon resistors

Figure 37: RX Analog Front End

+

–

+

–

UltraScale DeviceBoard

ACJTAG RX

ACJTAG RX

50Ω

50Ω

MGTAVTT Programmable

FLOAT

MGTAVTT

MGTAVTT

~100 nF

~100 nF

PAD_RTERM_VCOM_MODE

PAD_RTERM_VCOM_LVL

X20922-111918

Ports and Attributes

The following table denes the RX AFE ports.

Table 48: RX AFE ports

Ports Dir Clock Domain Description

CH[0/1]_GTMRXP,

CH[0/1]_GTMRXN

In (Pad) RX Serial Clock Differential complements of one another

forming a differential receiver input pair.

These ports represent pads. The location

of these ports must be constrained (see

Implementation) and brought to the top

level of the design.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 85

Loading...

Loading...