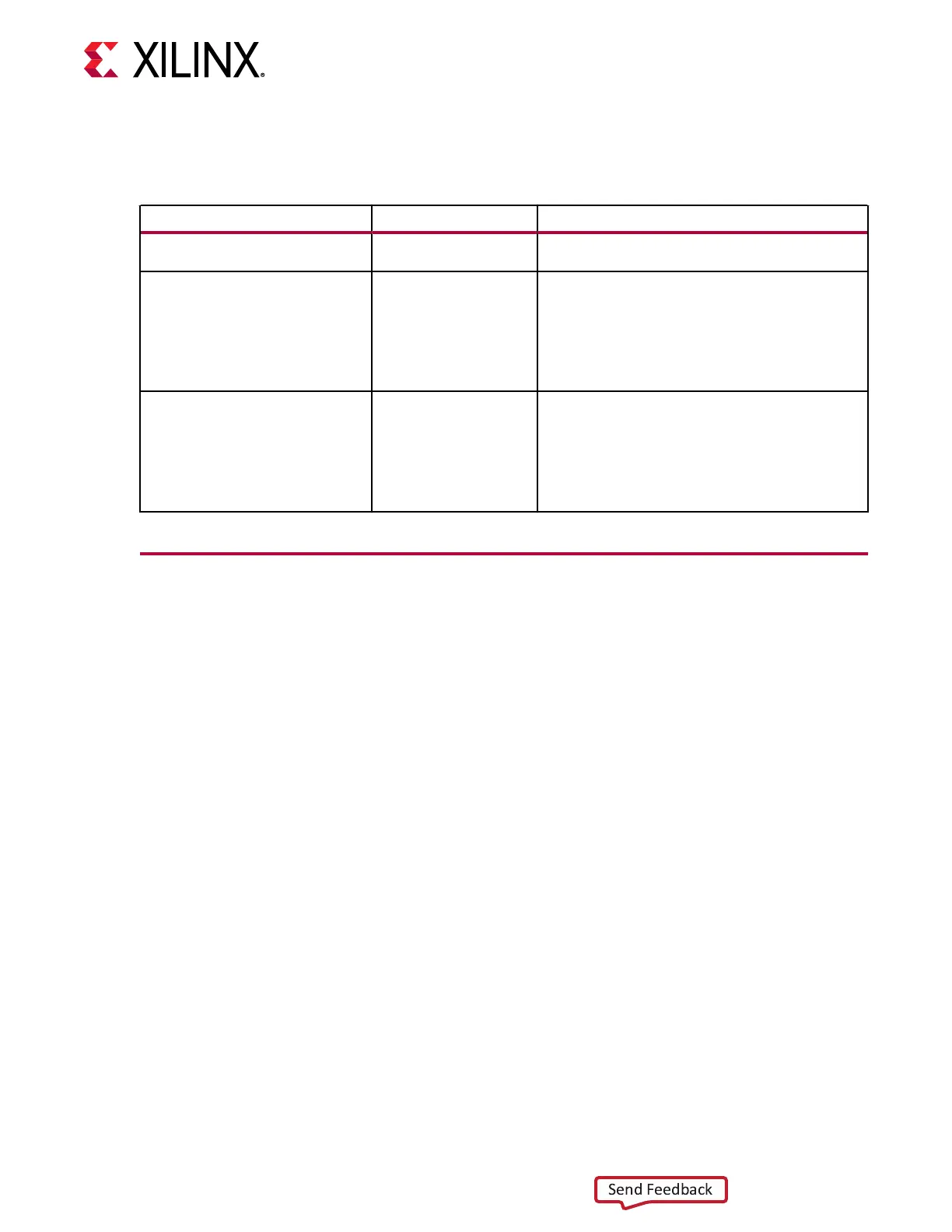

The following table denes the RX buer aributes.

Table 65: RX Buffer Attributes

Attribute Type Description

CH[0/1]_RX_PCS_CFG0 16-bit Binary Reserved. Use the recommended value from the

Wizard.

CH[0/1]_RXFIFO_UNDERFLOW 1-bit Binary A value of 1 indicates FIFO underflow.

For channel 0, bit[8] of DRP Address 0x48B.

For channel 1, bit[8] of DRP Address 0x68B.

Note: This is a read-only aribute.

CH[0/1]_RXFIFO_OVERFLOW

1-bit Binary A value of 1 indicates FIFO overflow.

For channel 0, bit[9] of DRP Address 0x48B.

For channel 1, bit[9] of DRP Address 0x68B.

Note: This is a read-only aribute.

RX FEC

The Integrated KP4 Reed-Solomon Forward Error Correcon (RS-FEC) provides a robust mul-bit

error detecon/correcon algorithm that protects up to 2 x 58 Gb/s or 1x116 Gb/s electrical and

opcal links. This secon describes the operaon of the Integrated KP4 RS-FEC within the

UltraScale+™ device GTM transceivers.

KP4 FEC is based on the RS(544,514) code, which encodes message blocks of 5140 bits to

produce codewords of 5440 bits. For a detailed descripon of the RS-FEC sublayer in Ethernet,

including the denion of the KP4 FEC code, refer to clause 91 of the IEEE Standard for Ethernet

(IEEE Std 802.3-2015). The same FEC code is used in other standards such as OTN FlexO and

Interlaken.

The Integrated KP4 RS-FEC for each GTM dual is composed of two logical slices for each

channel. These can operate as two independent RS-FEC processing units at up to 58 Gb/s each,

or as one unied unit at up to 116 Gb/s. When operang at up to 116 Gb/s, data is transmied

and received over four virtual FEC lanes as described in IEEE 802.3-2015 clause 91. When

operang as 2 x 58 Gb/s, data can be transmied and received over two virtual FEC lanes per

58 Gb/s channel, or as a raw data stream (one virtual lane) with oponal PN scrambling for

backplane operaons. The general principle of operaon of the FEC is the same whichever mode

is chosen.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 106

Loading...

Loading...