Ports and Attributes

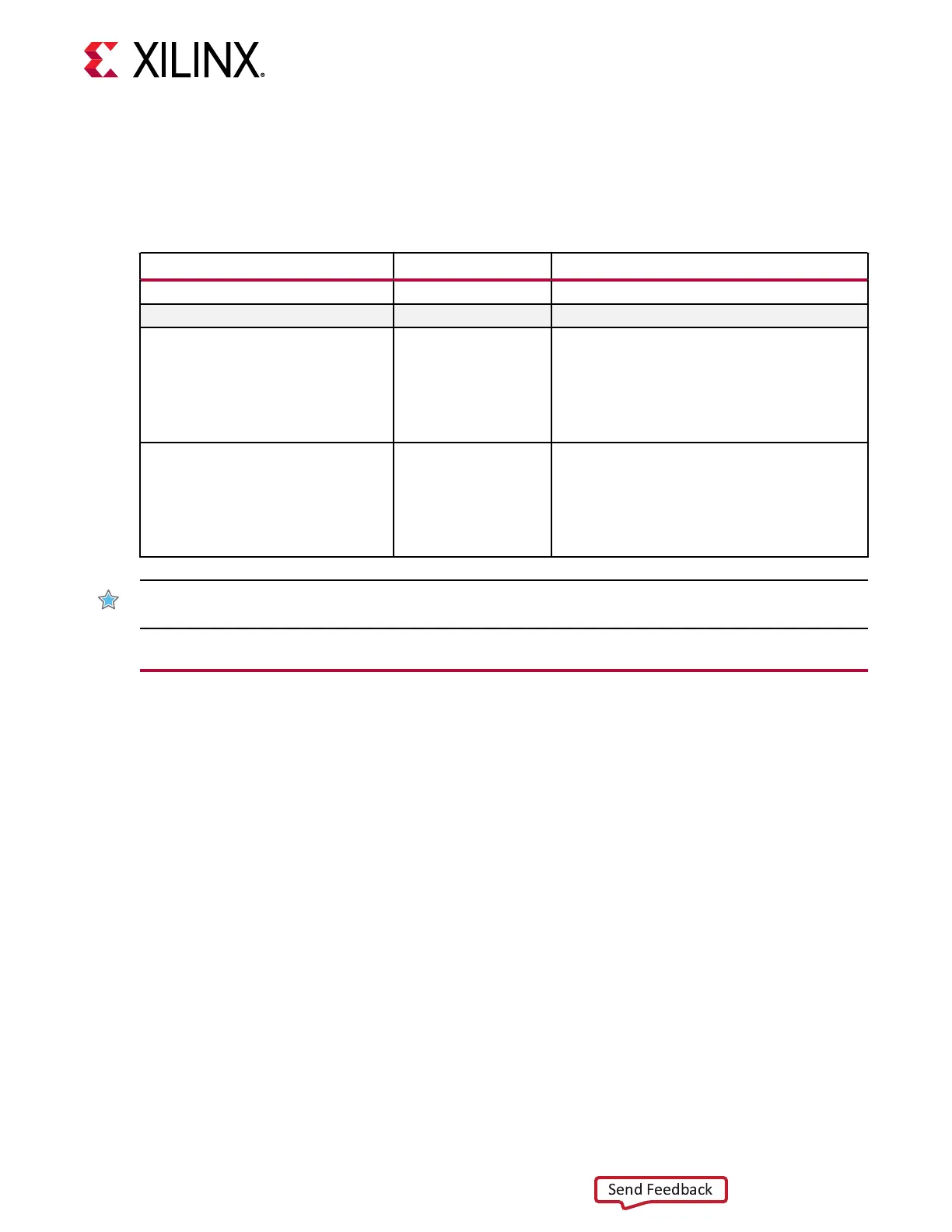

The following table denes the aributes required for RX Gray Encoder control.

Table 58: Gray Encoder Attributes

Attribute Type Description

CH[0/1]_RX_PCS_CFG0 16-bit Reserved.

Bit Name Address Description

RX_GRAY_ENDIAN [13] In PAM4 mode, this attribute controls the received

endianness. In NRZ mode, the default Wizard value

must be used.

1’b0: Non-inverting.

1’b1: Inverting.

RX_GRAY_BYP_EN

[12] In PAM4 mode, this attribute enables Gray

encoding. In NRZ mode, the default Wizard value

must be used.

1’b0: Enables Gray encoding.

1’b1: Disables Gray encoding.

IMPORTANT! In PAM4 mode, if the Gray Encoder is enabled for the receiver, the transmier Gray

Encoder should also be enabled for proper data recovery.

RX Polarity Control

If the RXP and RXN dierenal traces are accidentally swapped on the PCB, the dierenal data

received by the GTM RX is reversed. The GTM RX allows inversion to be done on parallel bytes

in the PCS aer the SIPO to oset reversed polarity on the dierenal pair. The polarity control

funcon uses the CH0_RXPOLARITY and CH1_RXPOLARITY input, which is driven High from

the interconnect logic interface to invert polarity.

Ports and Attributes

The following table denes the ports required for RX polarity control.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 100

Loading...

Loading...