Chapter 4

Receiver

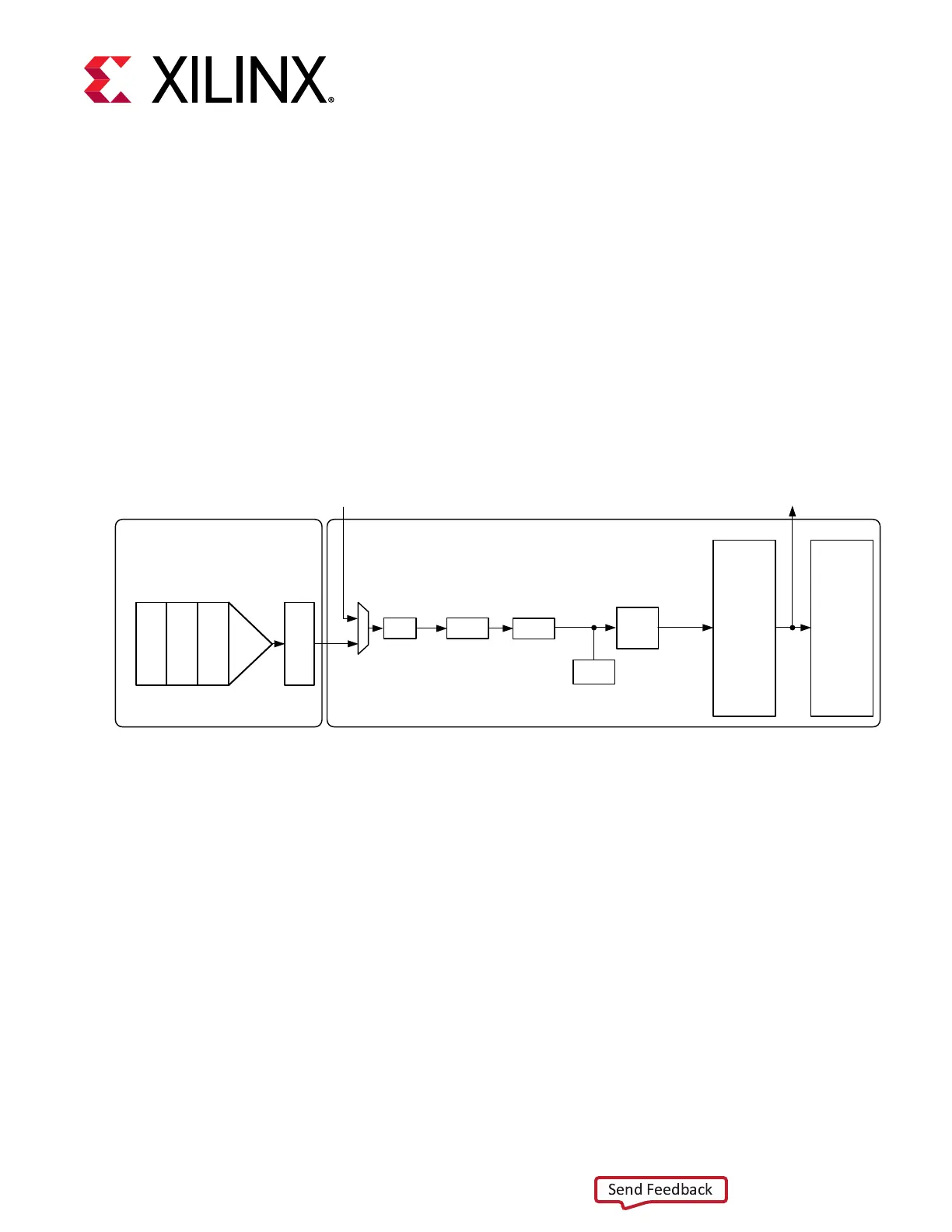

This secon shows how to congure and use each of the funconal blocks inside the receiver

(RX). Each GTM transceiver includes an independent receiver made up of a PCS and PMA. The

following gure shows the blocks of the GTM transceiver RX. High-speed serial data ows from

traces on the board into the PMA of the GTM transceiver RX, into the PCS, and nally into the

interconnect logic.

Figure 36: GTM Transciever RX Block Diagram

Polarity

FIFO

PRBS

Checker

RX

Interface

FEC

Gray

Encoder

Pre-

Coder

RX PCS

DFE/

FFE

RX EQ SIPOADC

RX PMA

To RX Parallel Data

(Near-End PCS Loopback)

From RX Parallel Data

(Far-End PCS Loopback)

X20221-053018

The key elements within the GTM transceiver RX are:

1. RX Analog Front End

2. RX Equalizer

3. RX CDR

4. RX Fabric Clock Output Control

5. RX Margin Analysis

6. RX Pre-Coder

7. RX Gray Encoder

8. RX Polarity Control

9. RX Paern Checker

10. RX Buer

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 84

Loading...

Loading...