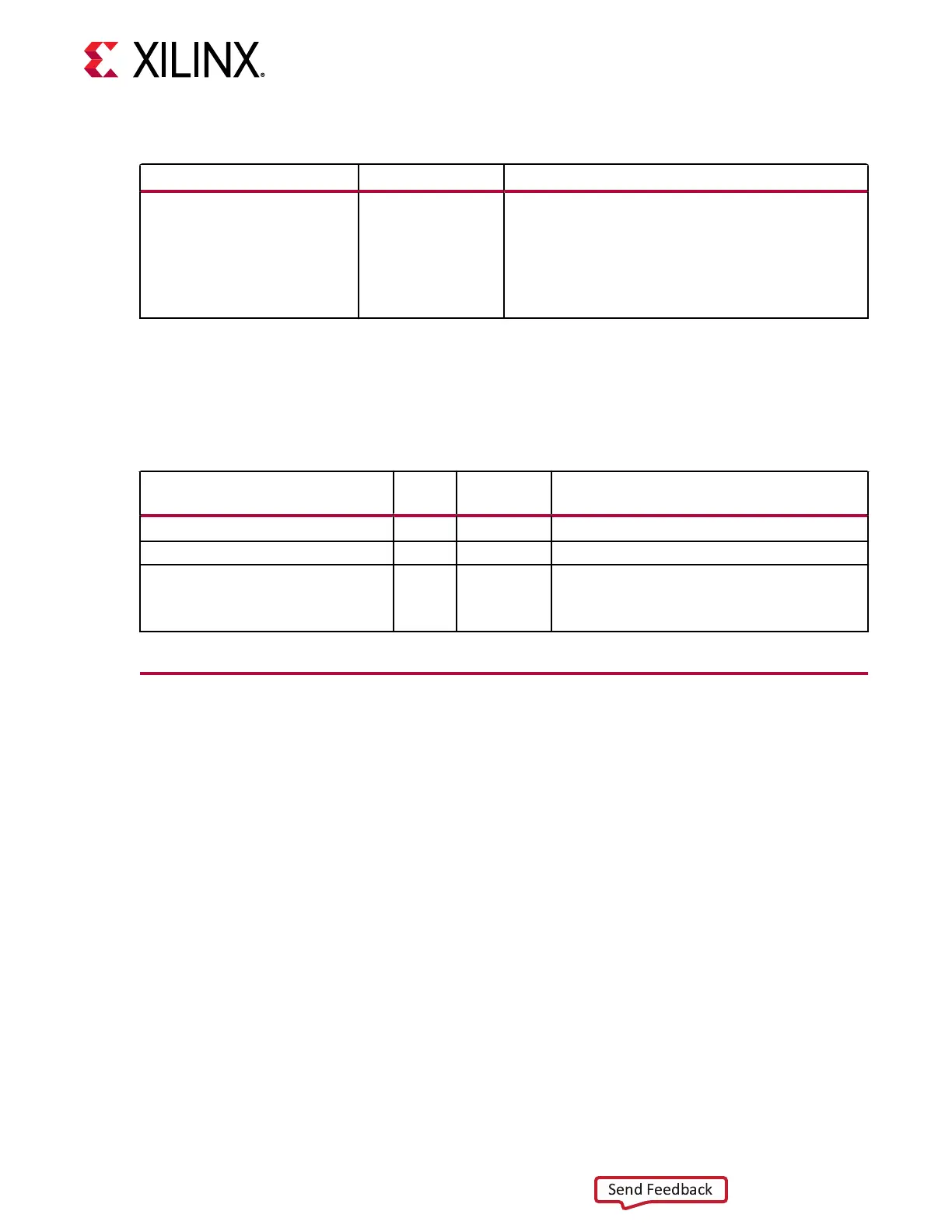

Table 44: TX Programmable Divider Attribute (cont'd)

Attribute Type Description

TX_PROGDIV_PDBV_DIV5 [2] This attribute is used during the TX programmable divider

ratio selection.

• The attribute must be set to 1’b0 when the desired

divider value is either 16.5, 33, 66, or 132.

• For all other divider values, this should be set to 1’b1.

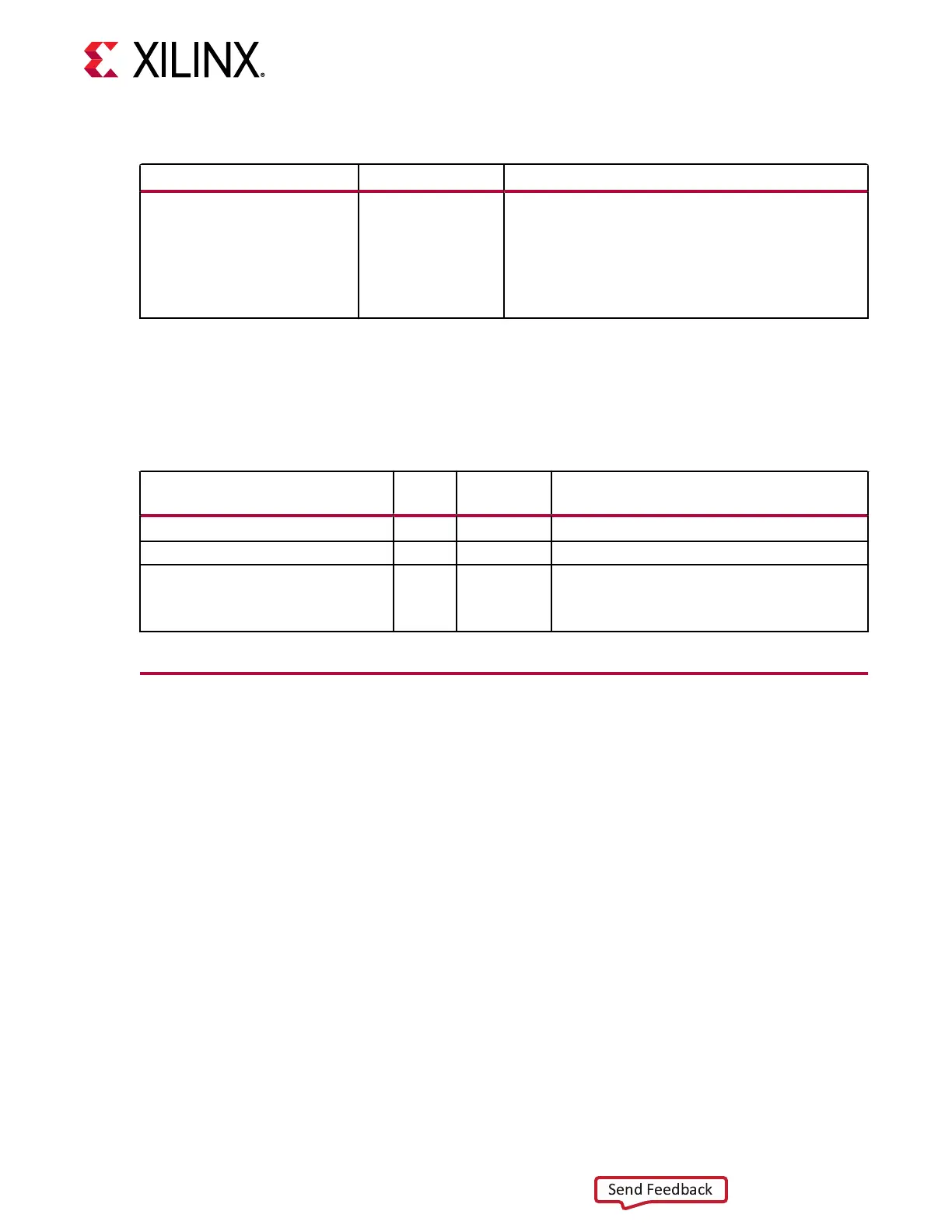

Ports and Attributes

The following table denes the ports required for TX fabric clock output control.

Table 45: TX Fabric Clock Output Control Ports

Port Dir

Clock

Domain

Description

CH[0/1]_TXOUTCLKSEL[2:0] In Async This port must be set to 3'b000.

CH[0/1]_TXOUTCLK Out Clock Reserved.

CH[0/1]_TXPROGDIVCLK Out Clock TXPROGDIVCLK is the parallel output clock from the

TX programmable divider. This clock is the

recommended output to the interconnect logic

through BUFG_GT.

TX Configurable Driver

The GTM transceiver TX driver is a high-speed voltage-mode dierenal output buer. To

maximize signal integrity, it includes these features:

• Dierenal voltage control

• Two pre-cursor, and one post-cursor transmit pre-emphasis

• Two modulaon schemes: NRZ and PAM4

• Calibrated terminaon resistors

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 77

Loading...

Loading...