Ports and Attributes

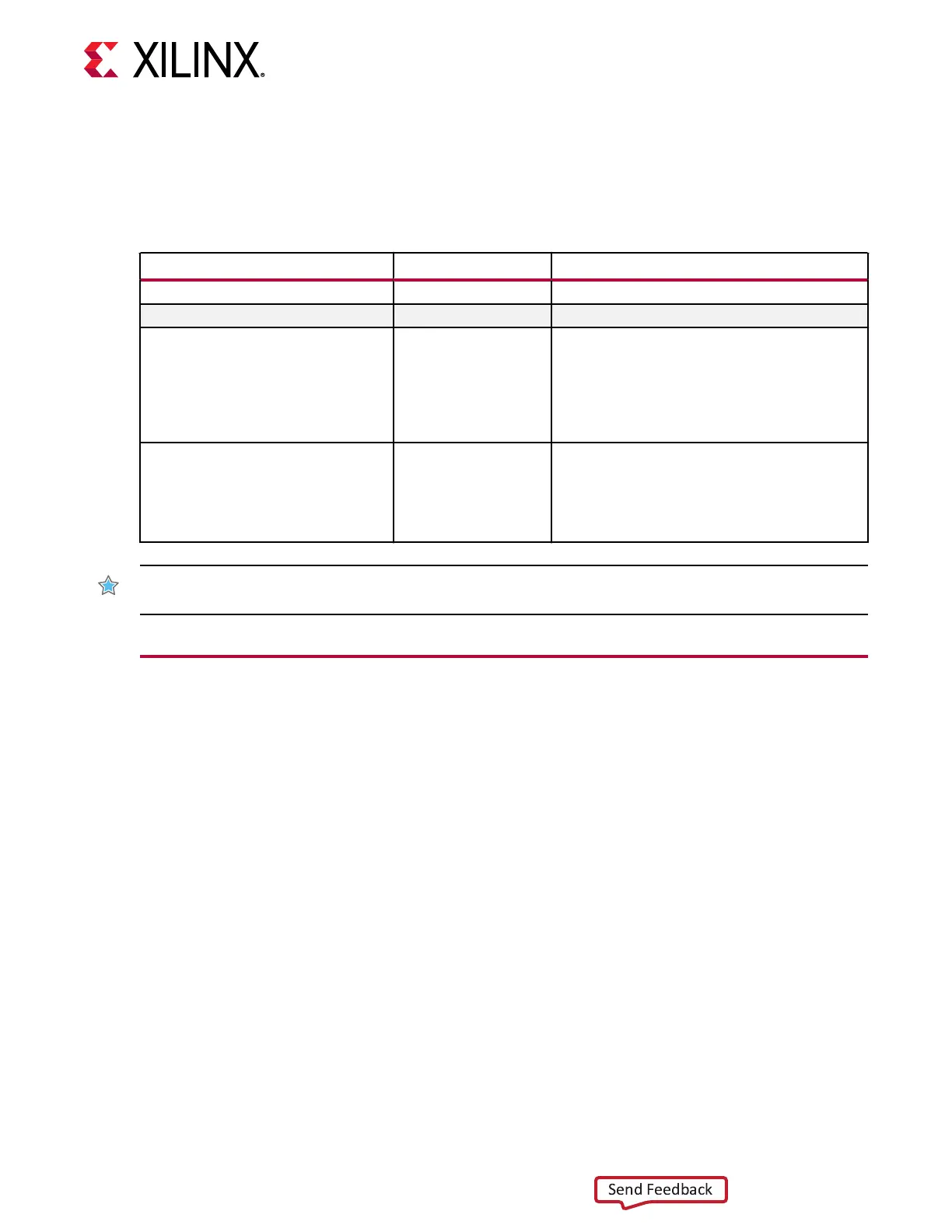

The following table denes the aributes required for TX pre-coder control.

Table 42: Pre-Coder Attributes

Attribute Type Description

CH[0/1]_TX_PCS_CFG0 16-bit Reserved.

Bit Name Address Description

TX_PRECODE_ENDIAN [11] In PAM4 mode, this attribute controls pre-coder

transmitted endianness. In NRZ mode, the default

Wizard value must be used.

1’b0: Non-inverting.

1’b1: Inverting.

TX_PRECODE_BYP_EN

[10] In PAM4 mode, this attribute enables pre-coding. In

NRZ mode, the default Wizard value must be used.

1’b0: Enables pre-code.

1’b1: Disables pre-code.

IMPORTANT! In PAM4 mode, if pre-coder is enabled for the transmier, the receiver pre-coder should

also be enabled for proper data recovery.

TX Fabric Clock Output Control

The TX Clock Divider Control block has two main components: serial clock divider control, and

parallel clock divider and selector control. The clock divider and selector details are illustrated in

the following gure.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 73

Loading...

Loading...