Ports and Attributes

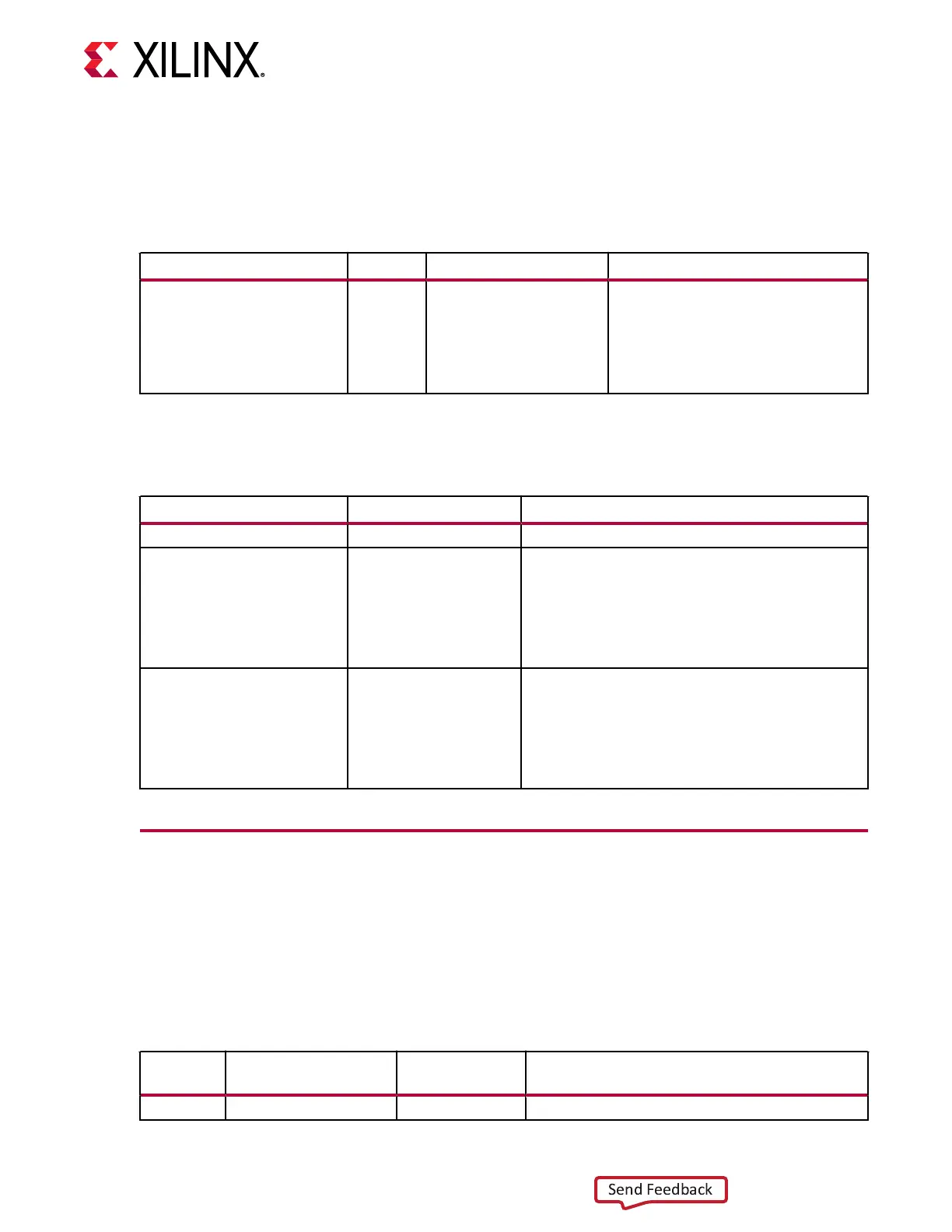

The following table denes the TX buer ports.

Table 35: TX Buffer Ports

Port Dir Clock Domain Description

CH[0/1]_TXBUFSTATUS[1:0] Out TXUSRCLK TX buffer status:

Bit[1]: FIFO overflow status. A value of

1 indicates FIFO overflow.

Bit[0]: FIFO underflow status. A value

of 1 indicates FIFO underflow.

The following table

denes the TX buer aributes.

Table 36: TX Buffer Attributes

Attribute Type Description

CH[0/1]_TX_PCS_CFG0 16-bit Reserved. Use the recommended value from the Wizard.

CH[0/1]_TXFIFO_UNDERFLOW 1-bit A value of 1 indicates FIFO underflow.

For channel 0, bit[8] of DRP address 0x489

For channel 1, bit[8] of DRP address 0x689

Note: This is a read-only aribute.

CH[0/1]_TXFIFO_OVERFLOW

1-bit A value of 1 indicates FIFO overflow.

For channel 0, bit[9] of DRP address 0x489

For channel 1, bit[9] of DRP address 0x689

Note: This is a read-only aribute.

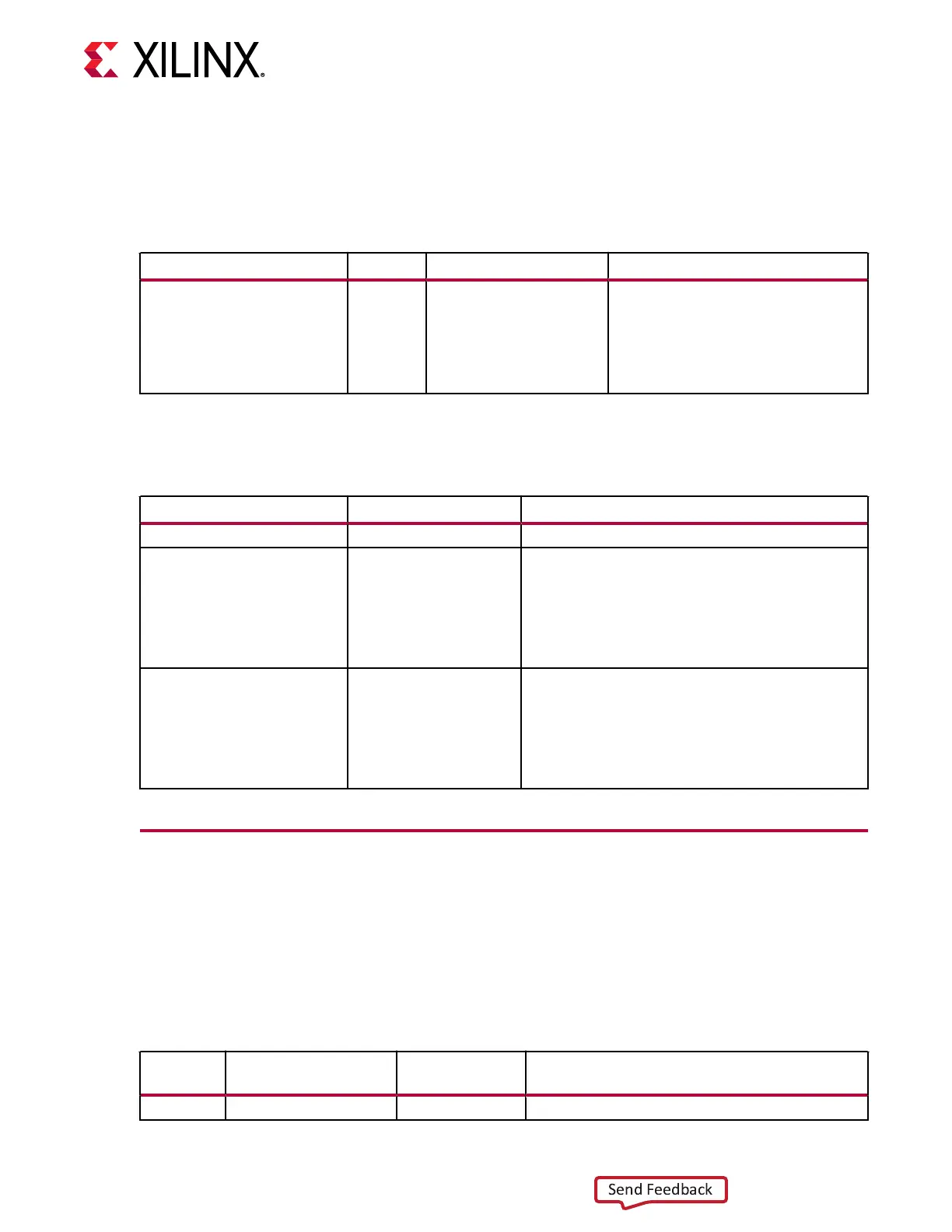

TX Pattern Generator

Pseudo-random it sequences (PRBS) are commonly used to test the signal integrity of high-speed

links. These sequences appear random but have specic properes that can be used to measure

the quality of a link. The GTM transceiver paern generator block can generate several industry-

standard PRBS paerns listed in the following table.

Table 37:

Supported PRBS Patterns

Name Polynomial

Length of

Sequence

Description

PRBS-7 1 + x

6

+ x

7

2

7

– 1 bits Used to test channels with 8B/10B.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 67

Loading...

Loading...