Table 37: Supported PRBS Patterns (cont'd)

Name Polynomial

Length of

Sequence

Description

PRBS-9 1 + x

5

+ x

9

2

9

– 1 bits ITU-T Recommendation O.150, Section 5.1. PRBS-9 is one

of the recommended test patterns for SFP+.

PRBS-13 1 + x + x

2

+ x

12

+ x

13

2

9

– 1 bits IEEE Std P802.3bs D3.5 test requires QPRBS-13 test

pattern.

PRBS-15 1 + x

14

+ x

15

2

15

– 1 bits ITU-T Recommendation O.150, Section 5.3. PRBS-15 is

often used for jitter measurement because it is the

longest pattern the Agilent DCA-J sampling scope can

handle.

PRBS-23 1 + x

18

+ x

23

2

23

– 1 bits ITU-T Recommendation O.150, Section 5.6. PRBS-23 is

often used for non-8B/10B encoding schemes. It is one

of the recommended test patterns in the SONET

specification.

PRBS-31 1 + x

28

+ x

31

2

31

– 1 bits ITU-T Recommendation O.150, Section 5.8. PRBS-31 is

often used for non-8B/10B encoding schemes. It is a

recommended PRBS test pattern for 10 Gigabit Ethernet.

See IEEE Std 802.3ae-2002.

IMPORTANT! For PAM4 modulaon, QPRBS paerns are supported by sending a convenonal PRBS

paern with PAM4 and Gray Coding based on the OIF2014.230 CEI-56G-VSR-PAM4 specicaon.

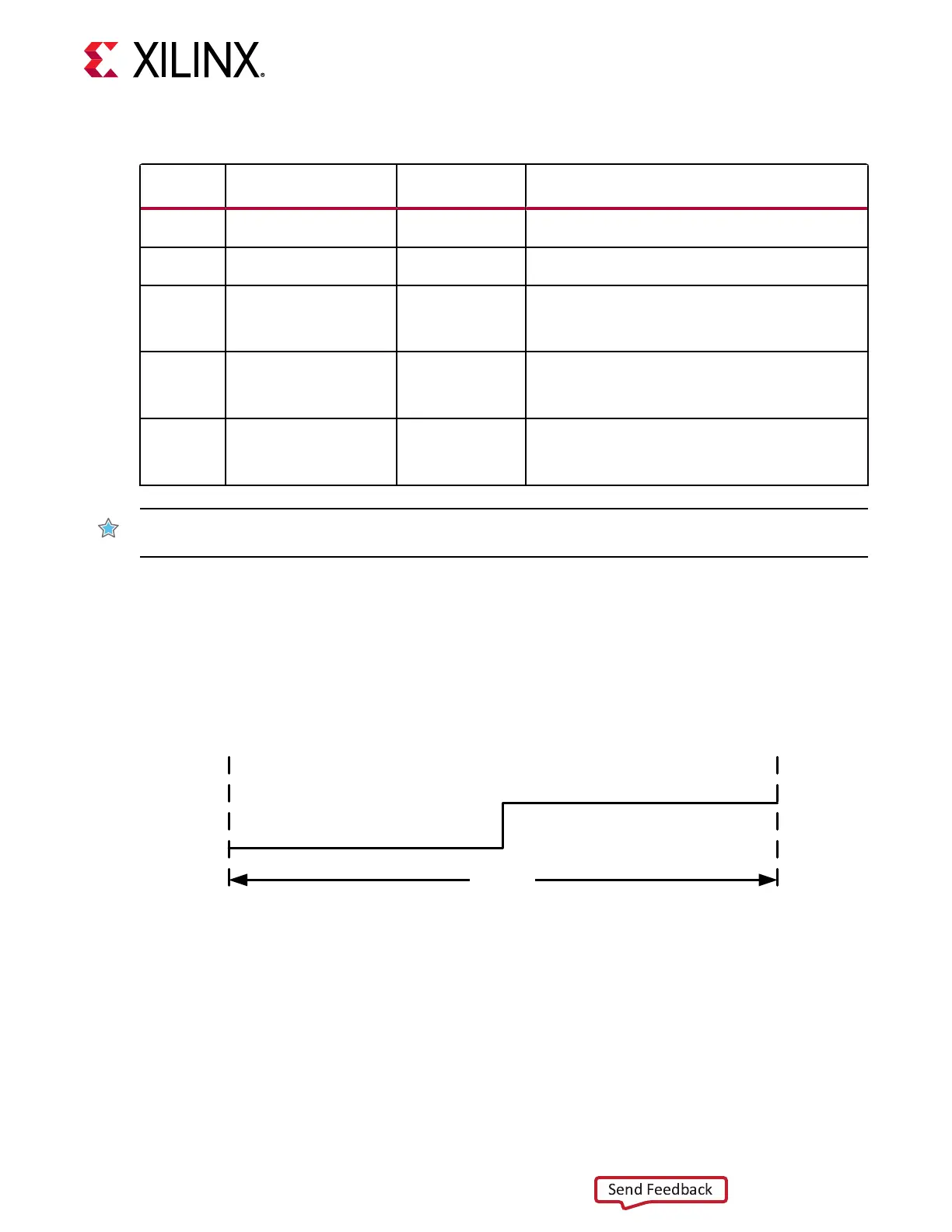

In addion to PRBS paerns, the GTM transceiver supports a 64 UI square wave test paern as

shown in the following gure, an alternang 1’b0 and 1’b1 (NRZ clock) test paern. Clocking

paerns are usually used to check PLL random jier oen done with a spectrum analyzer.

Note: For PAM4 modulaon, an alternang 1’b0 and 1’b1 test paern will not be a square wave due to

the amplitude modulaon mapping.

Figure 31: 64 UI Square Wave

64 UI

X22031-112618

The error inseron funcon is also supported to verify link connecon for jier tolerance tests.

When an inverted PRBS paern is necessary, the CH[0/1]_TXPOLARITY signal is used to control

polarity.

Chapter 3: Transmitter

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 68

Loading...

Loading...