When the RS-FEC is enabled in the receive direcon, data received by the GTM PMA and PCS is

passed to the Integrated KP4 RS-FEC. The RS-FEC then aligns and deskews the input lanes

according to the congured mode to reconstruct the transmied RS codeword stream. The RS-

FEC then performs RS decoding according to the 802.3bj clause 91 specicaon. The decoded

output data from the Integrated KP4 RS-FEC is then presented on the output of the GTM

transceiver to the fabric.

The Integrated KP4 RS-FEC does not navely perform transcoding, alignment marker removal,

alignment marker mapping, or alignment marker inseron operaons in the receive direcons. To

support protocols such as 100G Ethernet (IEEE 802.3 clause 91) and 50G Ethernet (IEEE 802.3

clause 134) which require 257b transcoding and alignment marker processing, the GTM Wizard

IP can oponally include so logic blocks for these funcons.

Ports and Attributes

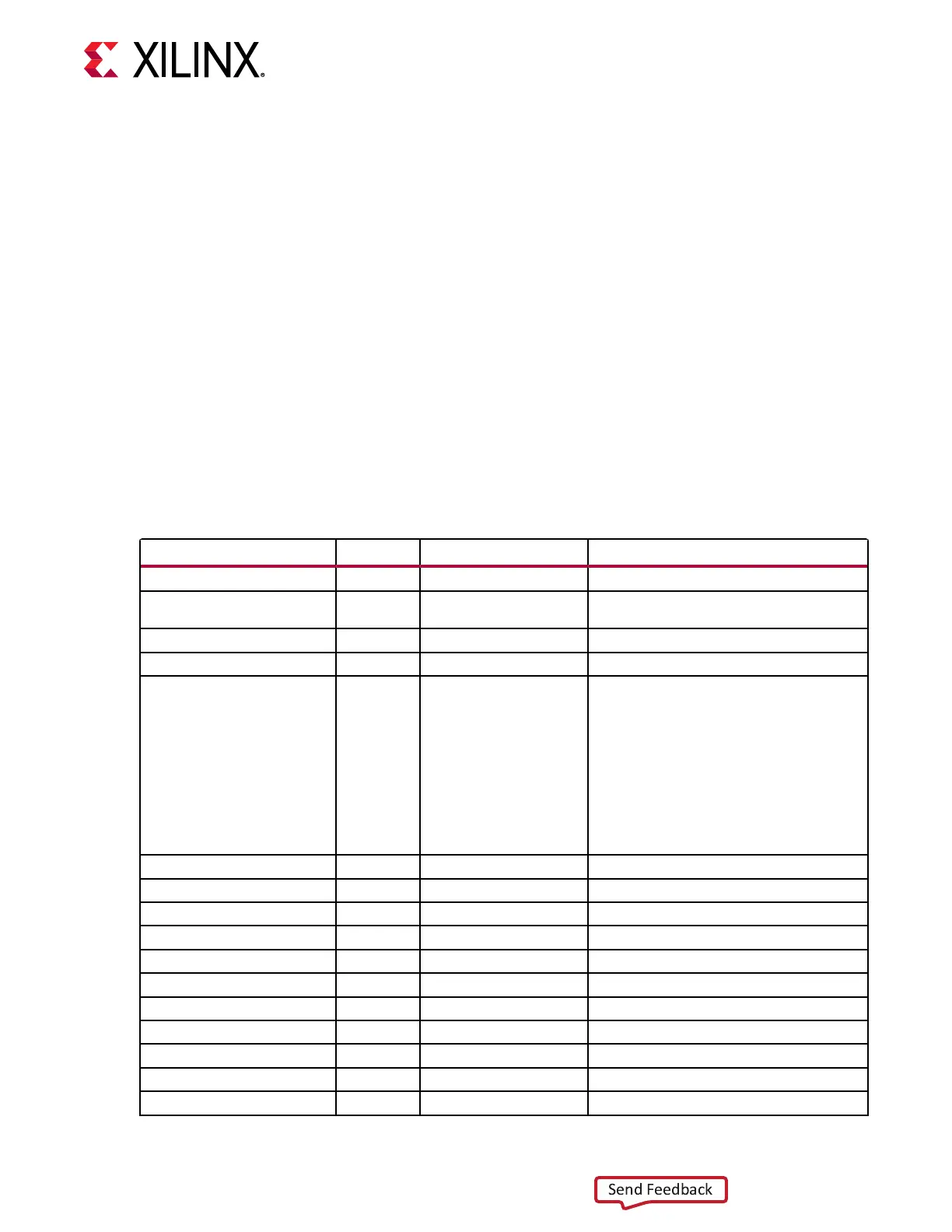

The following table shows the RX FEC-related ports for the GTM dual.

Table 66: RX FEC Ports

Ports Dir Clock Domain Description

CH[0/1]_RXFECRESET In Async Component reset port for RX FEC.

CH[0/1]_RXDATA[159:0] Out CH[0/1]_RXUSRCLK2 Output RX data. Must use 160-bit interface

when FEC is enabled.

CH[0/1]_RXDATASTART Out CH[0/1]_RXUSRCLK2 Start of codeword.

CH[0/1]_RXDATAISAM Out CH[0/1]_RXUSRCLK2 Alignment marker flag.

CH[0/1]_RXDATAFLAG[3:0] Out CH[0/1]_RXUSRCLK2 Codeword status flags:

Bit 0: When High, indicates the codeword

input to the decoder has no errors.

Bit 1: When High, indicates the codeword

input to the decoder has errors.

Bit 2: When High, indicates the codeword

output from the decoder has no errors.

Bit 3: When High, indicates the codeword

output from the decoder has errors.

FECCTRLRX0BITSLIPFS

In CH0_RXUSRCLK2 Bitslip control for slice 0.

FECCTRLRX1BITSLIPFS In CH1_RXUSRCLK2 Bitslip control for slice 1.

FECRX0ALIGNED Out CH0_RXUSRCLK2 Slice 0 alignment status.

FECRX1ALIGNED Out CH1_RXUSRCLK2 Slice 1 alignment status.

FECRX0CWINC Out CH0_RXUSRCLK2 Slice 0 codeword count increment.

FECRX1CWINC Out CH1_RXUSRCLK2 Slice 1 codeword count increment.

FECRX0CORRCWINC Out CH0_RXUSRCLK2 Slice 0 corrected codeword count increment.

FECRX1CORRCWINC Out CH1_RXUSRCLK2 Slice 1 corrected codeword count increment.

FECTRXLN0LOCK Out CH0_RXUSRCLK2 Lane 0 lock status.

FECTRXLN1LOCK Out CH0_RXUSRCLK2 Lane 1 lock status.

FECTRXLN2LOCK Out CH1_RXUSRCLK2 Lane 2 lock status.

Chapter 4: Receiver

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 107

Loading...

Loading...