Z8

®

CPU

User Manual

UM001604-0108 Interrupts

103

IRQ is always cleared to 00h and is read only until the first EI instruction, which enables

the IRQ to be read/written.

IMR is cleared before the IRQ enabling sequence to insure no unexpected interrupts occur

when EI is executed. This code sequence should be executed prior to programming the

application required values for IPR and IMR.

IRQ bits 6 and 7 are device dependent. When reserved, the bits are not used and return a 0

when read. When used as the Interrupt Edge select bits, the configuration options are as

listed in Table 21 on page 104.

EI // Enable IRQ register, otherwise read only.

// Not required if interrupts were previously enabled.

DI // Disable interrupt heading.

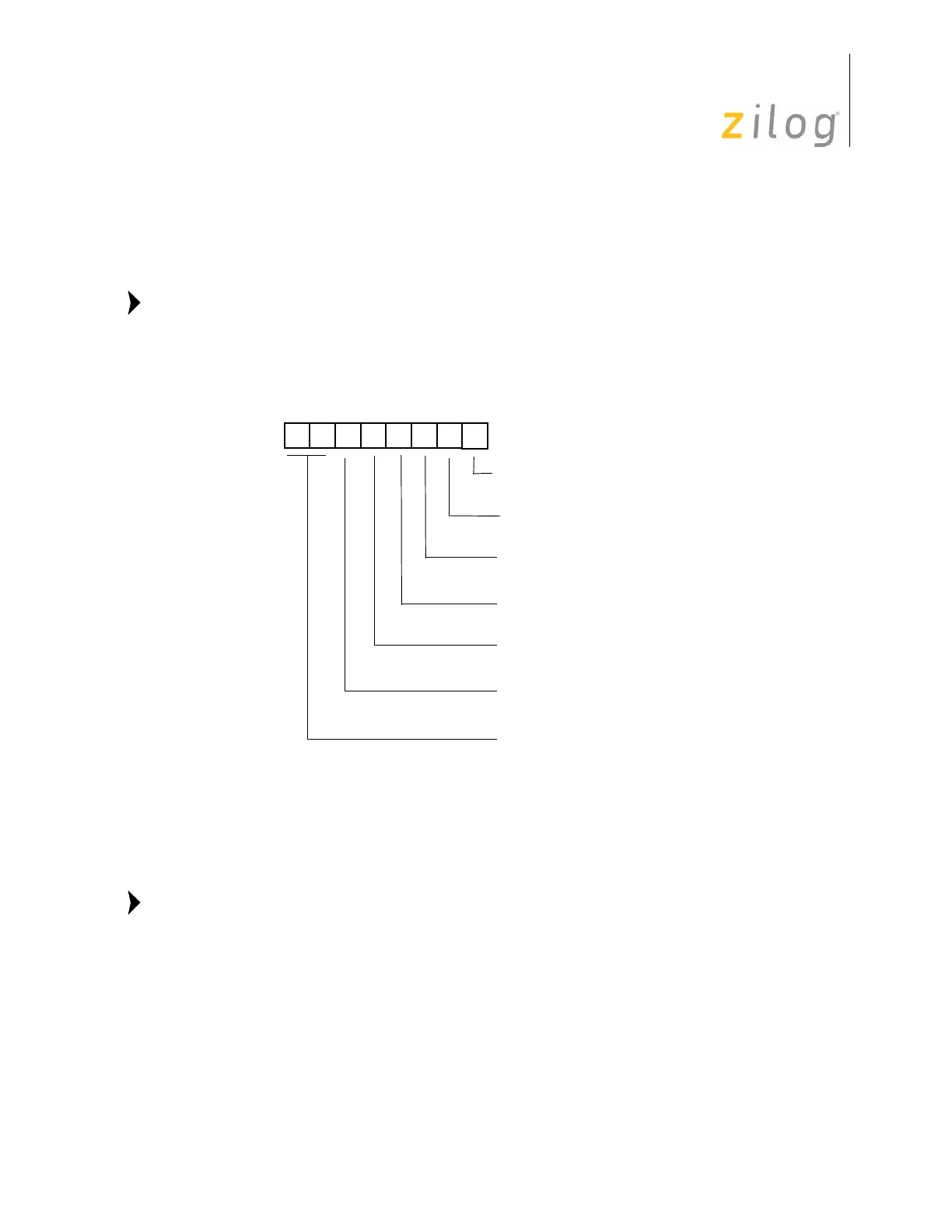

Figure 98. Interrupt Request Register

Note:

D7 D6 D5 D4 D3 D2 D1 D0

(Read/Write)

Reserved /Int Edge Select

Interrupt Request Register (IRQ)

Register FAh

0 = IRQ0 RESET

1 = IRQ0 SET

0 = IRQ1 RESET

1 = IRQ1 SET

0 = IRQ2 RESET

1 = IRQ2 SET

0 = IRQ3 RESET

1 = IRQ3 SET

0 = IRQ4 RESET

1 = IRQ4 SET

0 = IRQ5 RESET

1 = IRQ5 SET

Note:

Loading...

Loading...