Z8

®

CPU

User Manual

UM001604-0108 External Interface

136

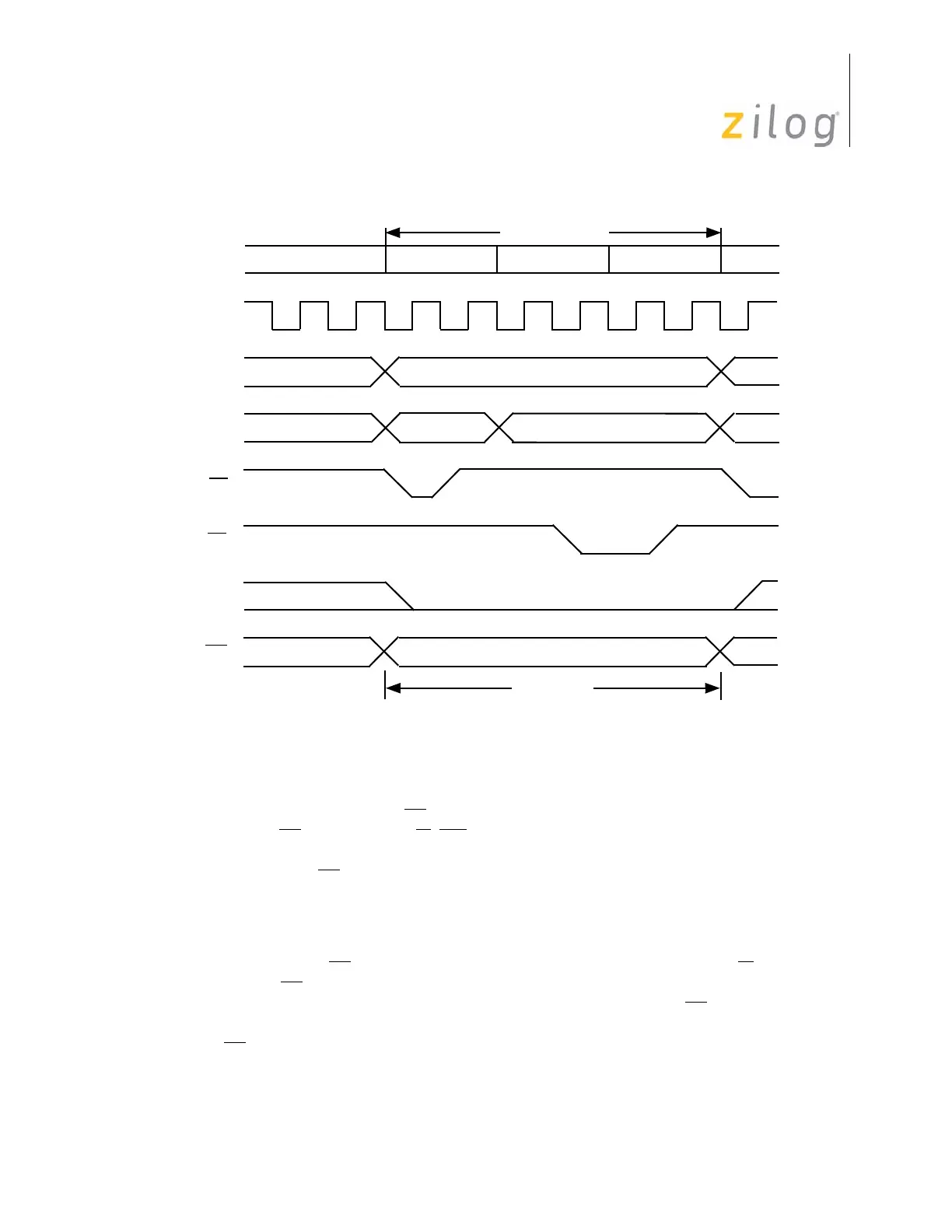

Address Strobe

All transactions start with AS driven Low and then raised High by Z8

®

CPU. The rising

edge of AS

indicates that R/W, DM (if used), and the address outputs are valid. The

address outputs (AD7–AD0), remain valid only during MnT1 and typically must be

latched using AS

. Address outputs (A15–A8) remain stable throughout the machine cycle,

regardless of the addressing mode.

Data Strobe

Z8

®

CPU uses DS to time the actual data transfer. For Write operations (R/W = Low), a

Low on DS

indicates that valid data is on the AD7–AD0 lines. For Read operations (R/W

= High), the bus is placed in a high-impedance state before driving DS

Low, so the

addressed device can put its data on the bus. The Z8 CPU samples this data prior to raising

DS

High.

Figure 127. External Memory Write Cycle

Machine Cycle

T1

T2

T3

Clock

A15-A8

AD7–AD0

AS

DS

R/W

DM

Write Cycle

A8-A15

A7–A0

D7–D0 OUT

Loading...

Loading...