Z8

®

CPU

User Manual

UM001604-0108 External Interface

137

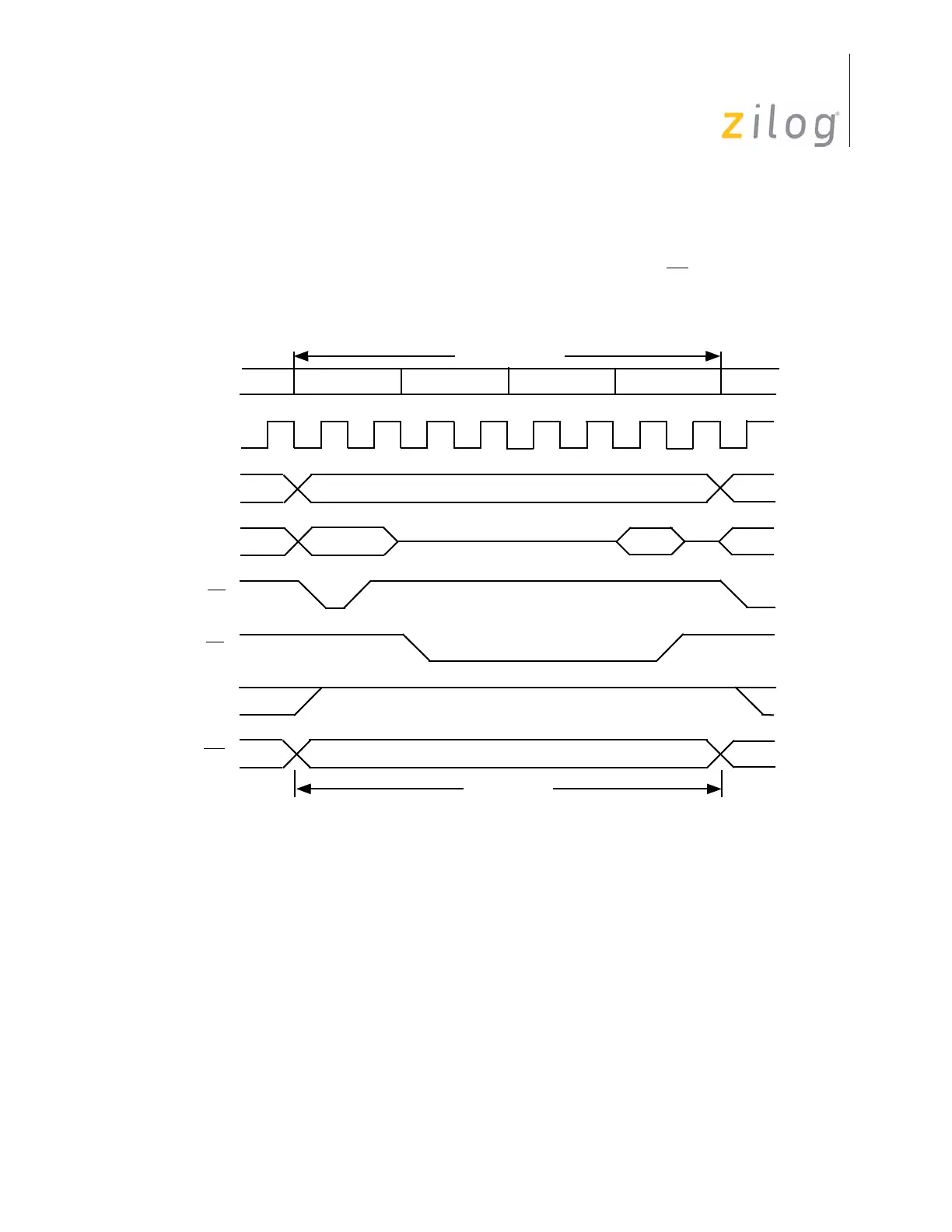

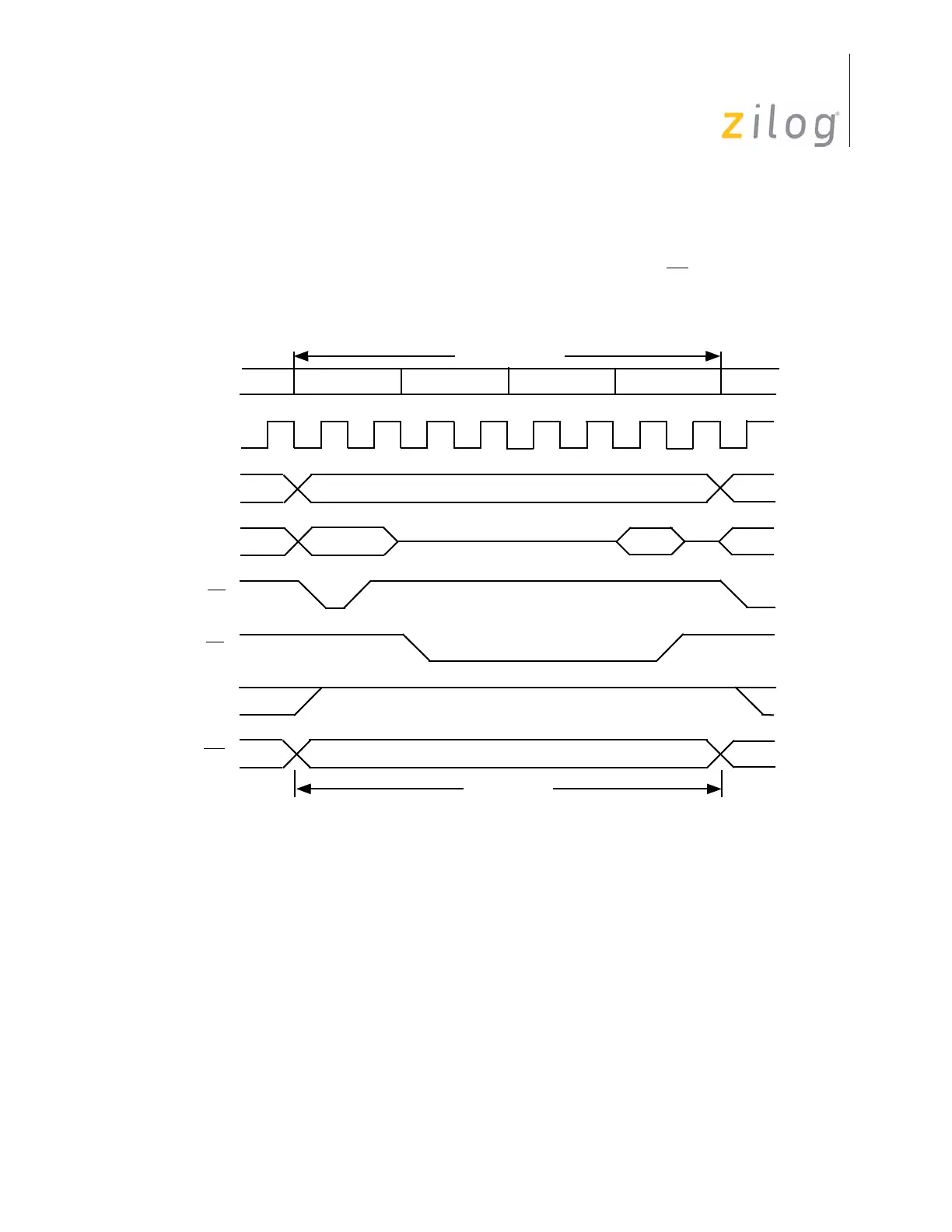

Extended Bus Timing

Some products can accommodate slow memory access time by automatically inserting an

additional software controlled state time (Tx). This stretches the DS

timing by two clock

periods. Figure 128 and Figure 129 on page 138 display extended external memory Read

and Write cycles.

Figure 128. Extended External Instruction Fetch or Memory Read Cycle

Machine Cycle

T2*

TX

T3

Clock

A15-A8

AD7–AD0

AS

DS

R/W

DM

Read Cycle

A15-A8

A7–A0

D7–D0 IN

T1

*

Port inputs are strobed during T2, which is two internal system clocks

before the execution of the current instruction.

Loading...

Loading...