Z8

®

CPU

User Manual

UM001604-0108 Input/Output Ports

45

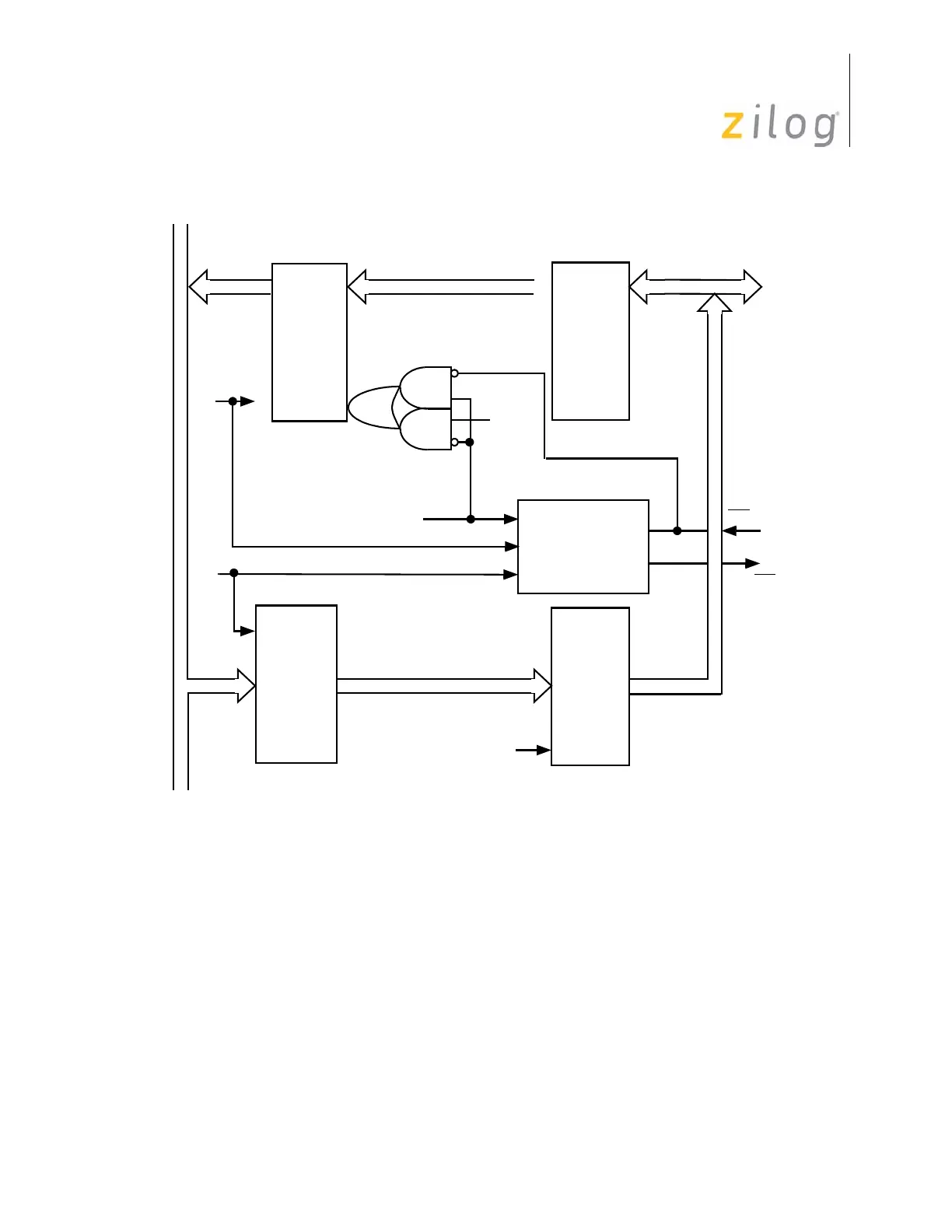

General I/O Mode

Port 0 can be an 8-bit, bidirectional, CMOS or TTL compatible I/O port. These eight I/O

lines can be configured under software control as a nibble I/O port (P03–P00 input/output

and P07–P04 input/output), or as an address port for interfacing external memory. The

input buffers can be Schmitt-Triggered, level shifted, or a single-trip point buffer and can

be nibble programmed. Either nibble output can be globally programmed as push–pull or

open-drain. Low EMI output buffers in some cases can be globally programmed by the

software as an OTP program option or as a ROM mask option. In such cases, the Z8

®

MCU features autolatches that are hardwired to the inputs. Refer to the specific Z8 MCU

product specification for the exact input/output buffer features that are available (see

Figure 30 on page 46 and Figure 31 on page 47).

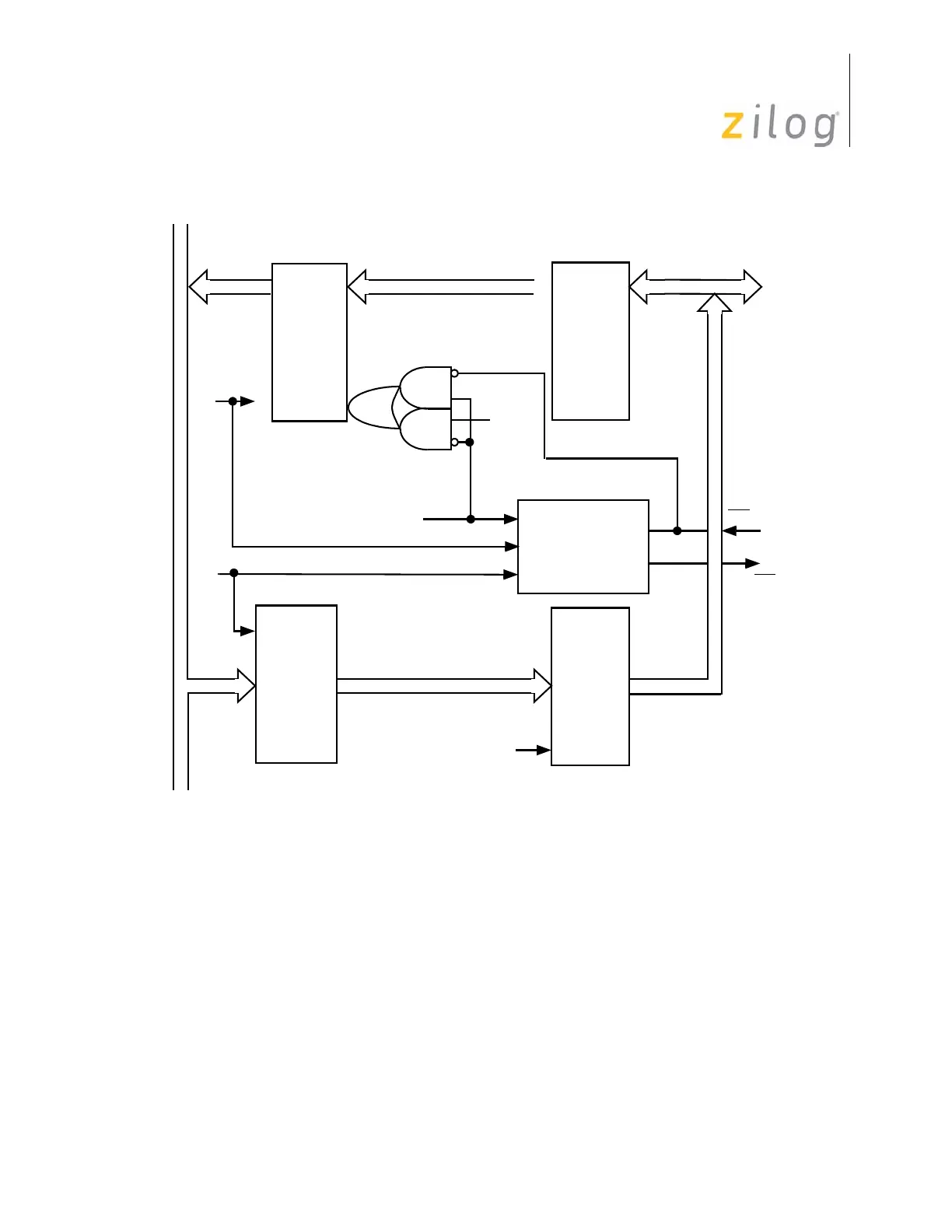

Figure 29. Ports 0, 1, 2 Generic Block Diagram

Handshake

Logic

Internal

Timing

Handshake

Selected

RDY/DAV

DAV/RDY

Port I/O

Lines

Input

Buffer

Input

Register

Handshake

Logic

Output

Buffer

Output

Register

Output

Enable

Internal

Bus

Write

Port

Read

Port

E

88

8

88

8

8

Loading...

Loading...