Z8

®

CPU

User Manual

UM001604-0108 Serial Input/Output

124

If the associated IRQ3 is enabled, an interrupt is generated. Bit 5 controls the clock phase

of the SPI. A 1 in bit 5 allows for receiving data on the clock’s falling edge and transmit-

ting data on the clock’s rising edge. A 0 allows receiving data on the clock’s rising edge

and transmitting on the clock’s falling edge. The SPI clock source is defined in bit 6. A 1

uses Timer0 output for the SPI clock, and a 0 uses TCLK for clocking the SPI. Finally, bit

7 determines whether the SPI is used as a Master or a Slave. A 1 puts the SPI into Master

mode and a 0 puts the SPI into Slave mode.

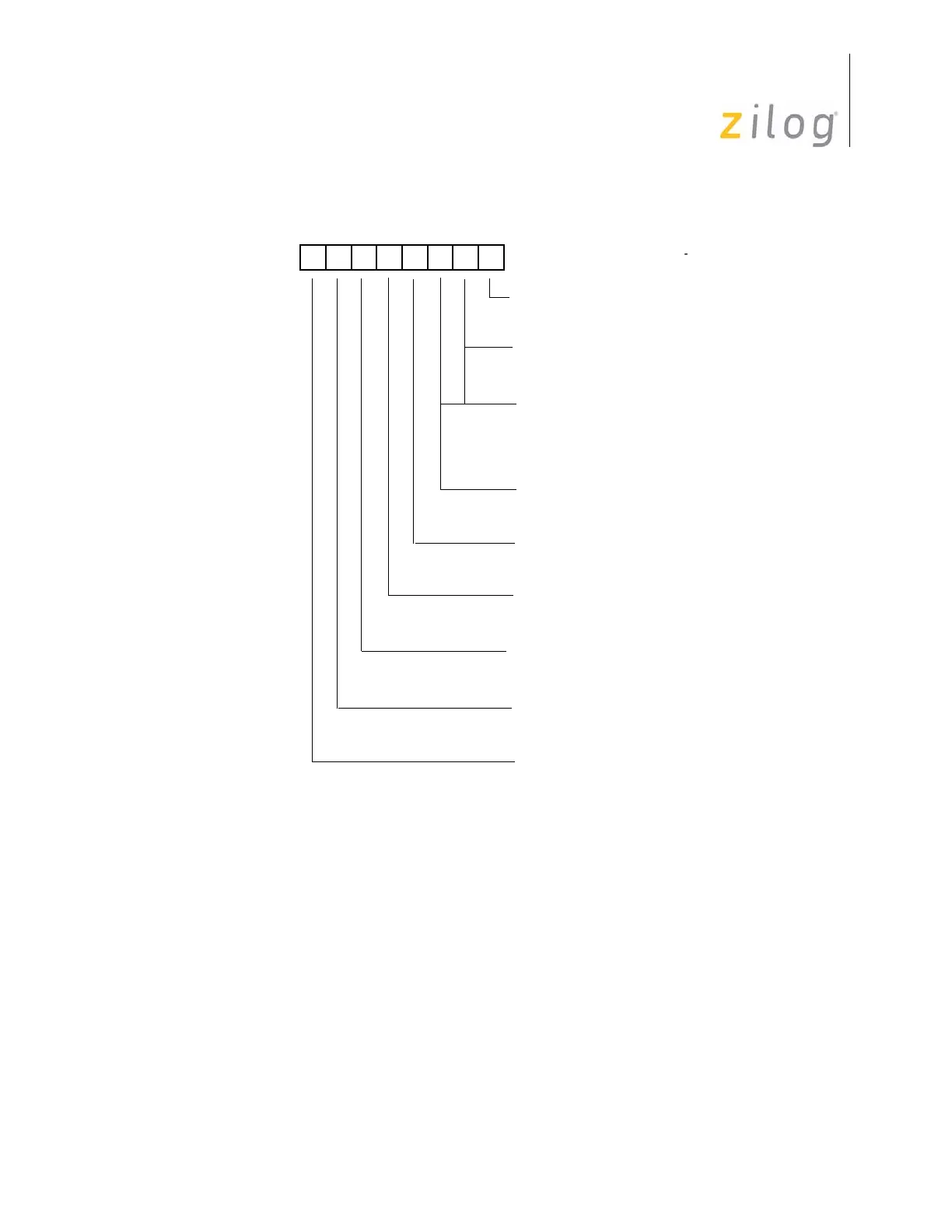

Figure 116. SPI Control Register

D7 D6 D5 D4 D3 D2 D1 D0

SCON (C) 02

CLK Divide (M)

00 TCLK/2

01 TCLK/4

10 TCLK/8

11 TCLK/16

DO SPI Port Enable (S)

0 SPI DO Port Enable

1 Do Port to I/O

0 Disable *

1 Enable

SPI Enable

0 Enable

1 Disable *

Compare Enable

0 Trans/Fall

1 Trans/Rise

Clock Phase

0 Reset

RxCharOverrun (S)

0 Reset

1 Char. Avail

RxCharAvail

1 Overrun

(M) Used with Bit D7 equal to 1

* Default setting after Reset

0 TCLK

1 Timer 0 Output

CLK Source

0 Slave

1 Master

Master Slave

(S) Used with Bit D7 equal to 0

Loading...

Loading...