Z8

®

CPU

User Manual

UM001604-0108 Instruction Description

172

Decimal Adjust

Syntax

DA dst

Instruction Format

Operation

dst ← DA dst

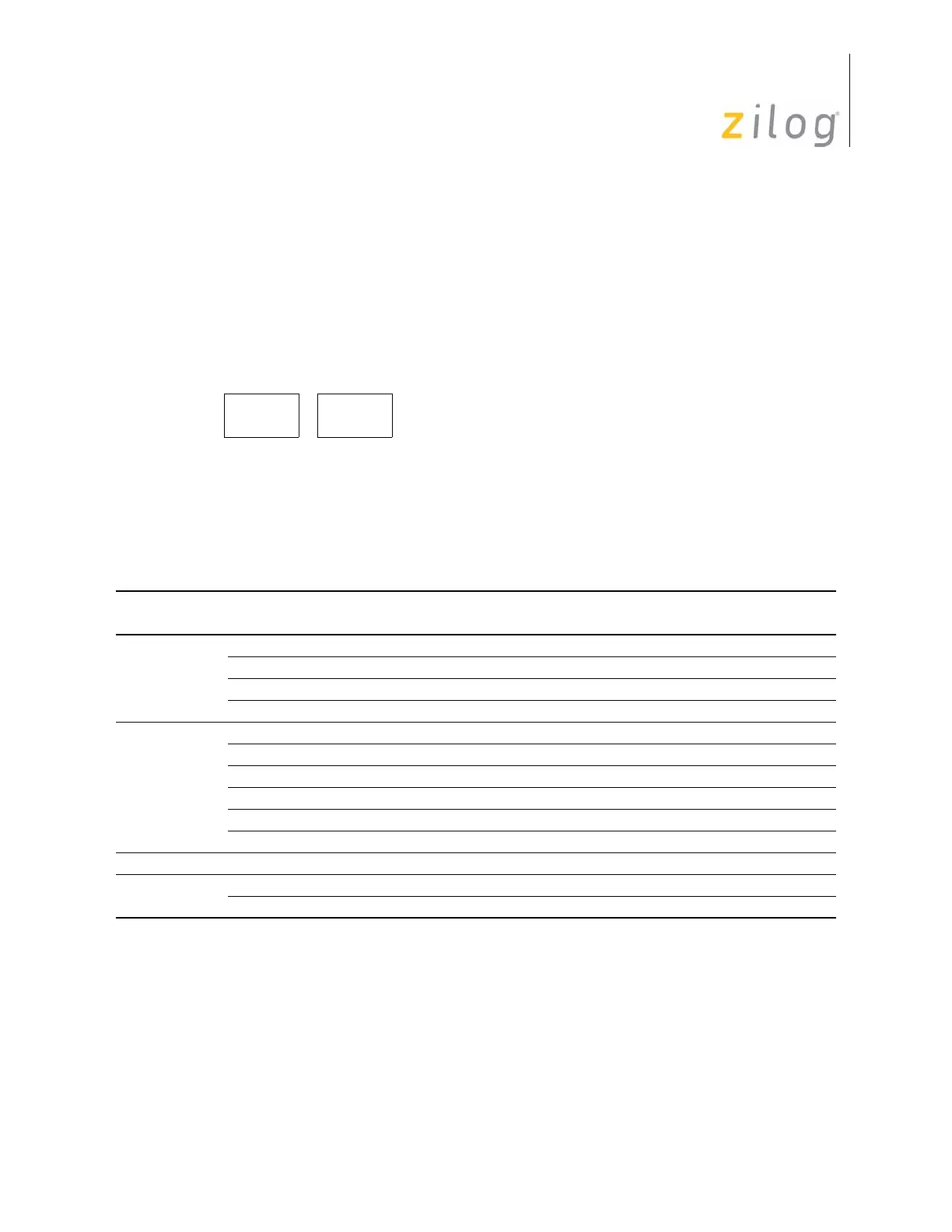

The destination operand is adjusted to form two 4-bit BCD digits following a binary addi-

tion or subtraction operation on BCD encoded bytes. For addition (ADD and ADC) or

subtraction (SUB and SBC), the following table indicates the operation performed.

If the destination operand is not the result of a valid addition or subtraction of BCD digits,

the operation is undefined.

Cycles

OPC

(Hex)

Address Mode

dst

OPC dst

840 R

841 IR

Instruction

Carry

Before DA

Bits 7–4

Value (Hex)

H Flag

Before DA

Bits 3–0

Value (Hex)

Number Added

To Byte

Carry After

DA

0 0–9 0 0–9 00 0

0 0–8 0 A–F 06 0

0 0–9 1 0–3 06 0

ADD 0 A–F 0 0–9 60 1

ADC 0 9–F 0 A–F 66 1

0 A–F 1 0–3 66 1

1 0–2 0 0–9 60 1

1 0–2 0 A–F 66 1

1 0–3 1 0–3 66 1

0 0–9 0 0–9 00 0

SUB 0 0–8 1 6–F FA 0

SBC 1 7–F 0 0–9 A0 1

1 6–F 1 6–F 9A 1

Loading...

Loading...