Z8

®

CPU

User Manual

UM001604-0108 Instruction Description

231

Shift Right Arithmetic

Syntax

SRA dst

Instruction Format

Operation

C ← dst(0)

dst(0) ← dst(1)

dst(1) ← dst(2)

dst(2) ← dst(3)

dst(3) ← dst(4)

dst(4) ← dst(5)

dst(5) ← dst(6)

dst(6) ← dst(7)

dst(7) ← dst(7)

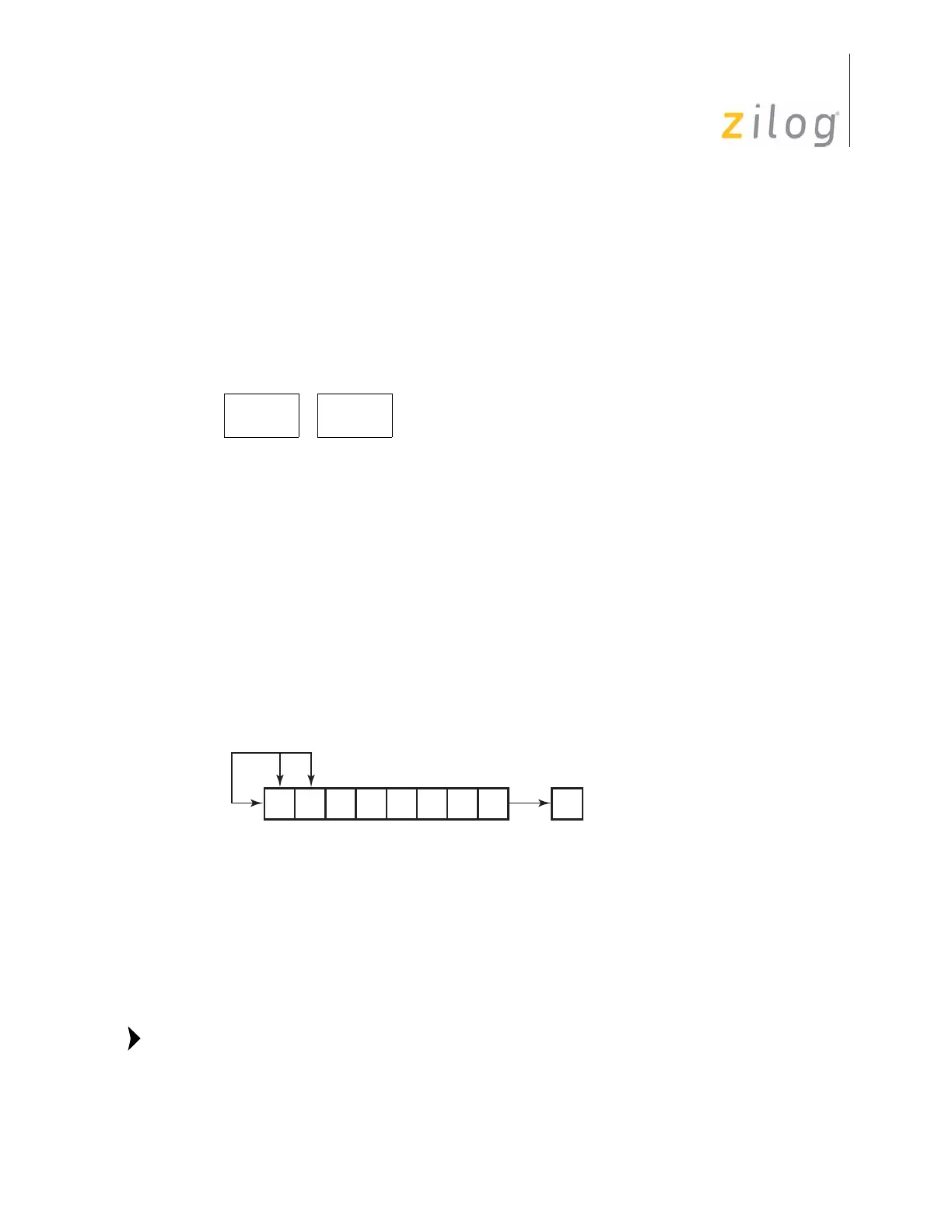

An arithmetic shift right by one bit position is performed on the destination operand. Bit 0

replaces the C Flag. Bit 7 (the Sign bit) is unchanged and its value is shifted into bit 6, as

shown below.

Address modes R or IR can be used to specify a 4-bit Working Register. In this format, des-

tination Working Register operand is specified by adding

1110b (Eh) to the high nibble of

Cycles

OPC

(Hex)

Address Mode

dst

OPC dst

6D0 R

6D1 IR

Flag Description

C Set if the bit rotated from the least significant bit position was 1 (that is, bit 0 was 1).

Z Set if the result is zero; cleared otherwise.

S Set if the result bit 7 is set; cleared otherwise.

V Always reset to 0.

D Unaffected

H Unaffected

CD7 D6 D5 D4 D3 D2 D1 D0

Note:

Loading...

Loading...