Z8

®

CPU

User Manual

UM001604-0108 Reset

34

Program execution starts 5 to 10 clock cycles after internal RESET has returned High. The

initial instruction fetch is from location

000Ch. Figure 22 on page 35 displays reset tim-

ing.

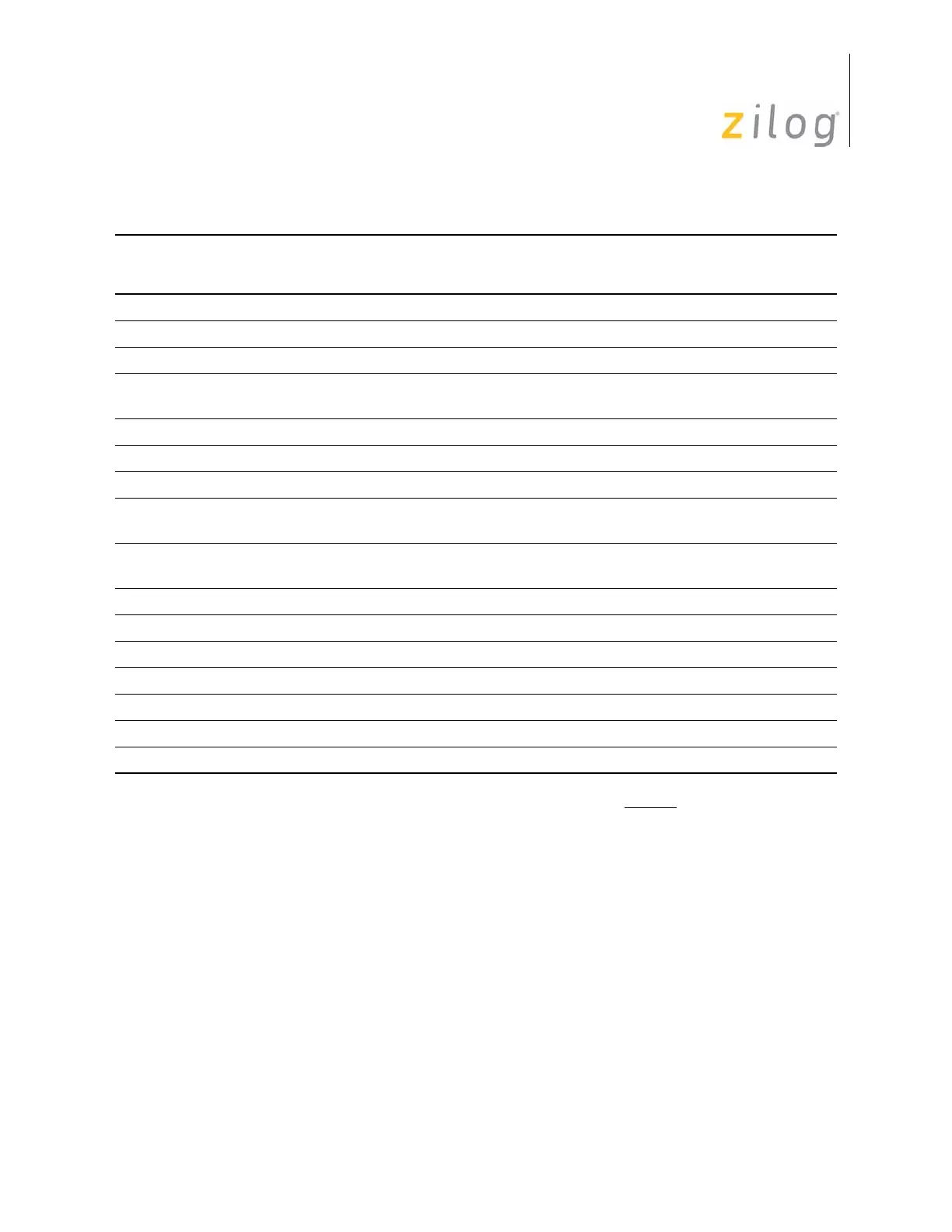

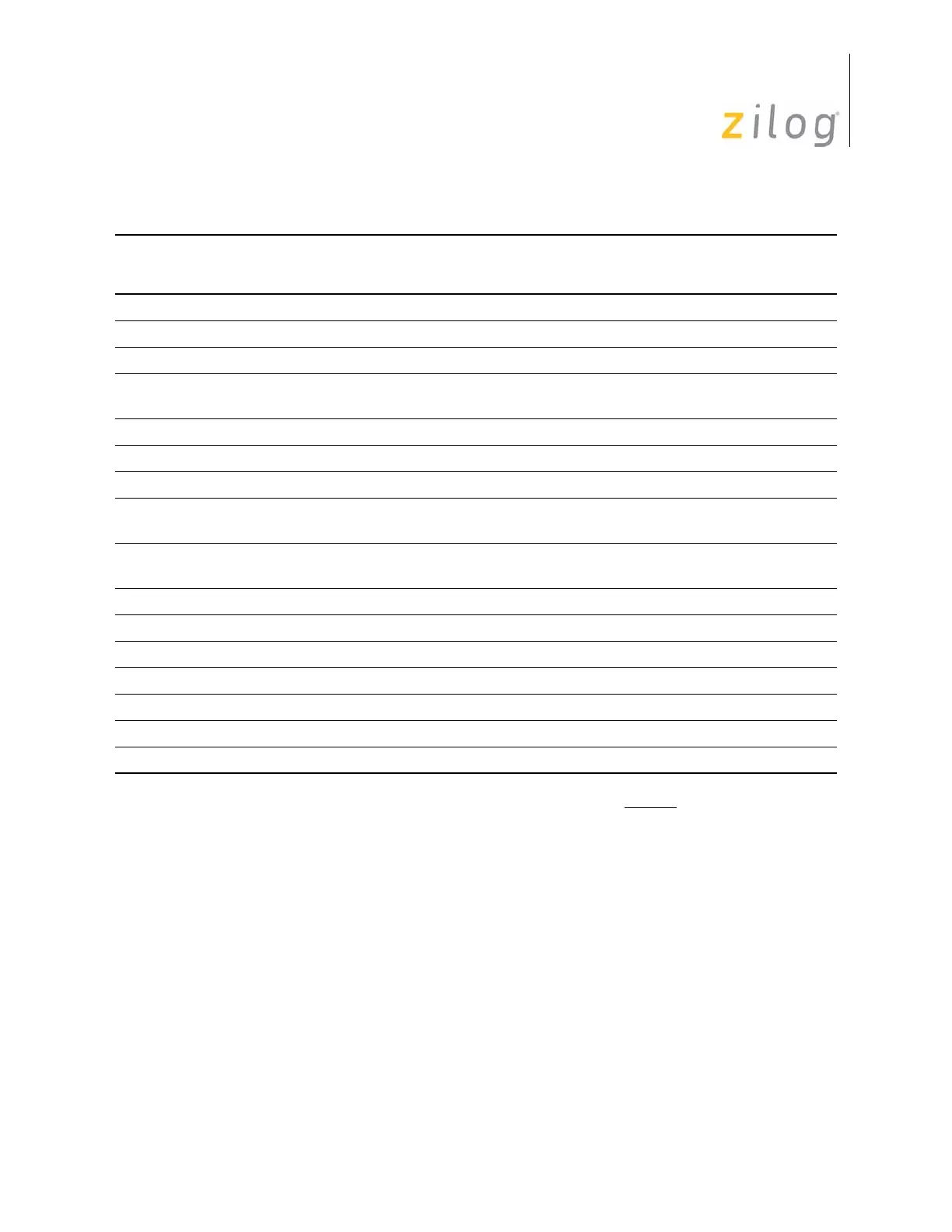

Table 12. Sample Control and Peripheral Register Reset Values (ERF Bank 0)

Register

(Hex) Register Name

Bits

Comments76543210

F0 Serial I/O UUUUUUUU

F1 Timer Mode 00000000Counter/Timers stopped.

F2 Counter/Timer1 UUUUUUUU

F3 T1 Prescaler UUUUUU0 0Single-pass count mode,

external clock source.

F4 Counter/Timer0 UUUUUUUU

F5 T0 Prescaler UUUUUUU0Single-pass count mode.

F6 Port 2 Mode 11111111All inputs.

F7 Port 3 Mode 00000000Port 2 open-drain, P33–P30

Input, P37–P34 Output.

F8 Port 0–1 Mode 01001101Internal Stack, Normal Memory

Timing.

F9 Interrupt Priority UUUUUUUU

FA Interrupt Request 00000000All Interrupts Cleared.

FB Interrupt Mask 0UUUUUUUInterrupts Disabled.

FC Flags UUUUUUUU

FD Register Pointer 00000000

FE Stack Pointer (High) UUUUUUUU

FF Stack Pointer (Low) UUUUUUUU

Loading...

Loading...