SERIAL INTERFACE

Reading

the

contents

of Read Registers 1 and 2 requires a

two

byte transfer operation.

The

first, a

write

operation to

the

commands/status

address location using

the

pointer

bits of Write Register a

to

specify

the

Read Register;

the

second,

the

actual

read operation from

the

same

address

to

access

the

contents

of

the

register. Following

any

read or

write

operation (apart from

writing

to Write Register

a),

the

address

pointer

within

the

SIO is always cleared to zero,

allowing

the

contents

of Read Register a to be accessed

using a single read operation.

The

definition of

each

register is detailed below.

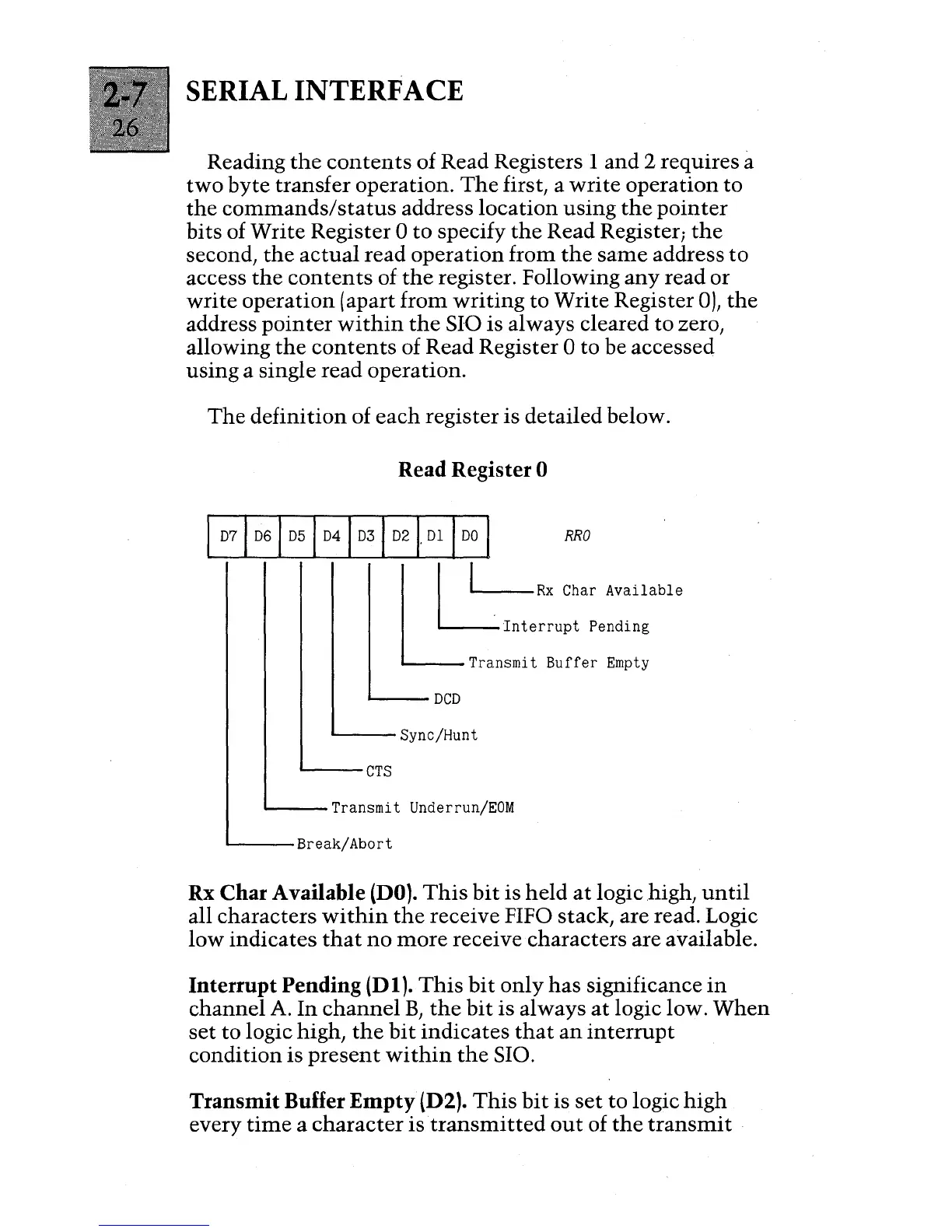

Read Register 0

I

D71 D61

D51

D41

D31

D21·

D 1 I

DO

I

RRO

lJ:

1 I

Rx

Char

Available

Interrupt

Pending

Transmit

Buffer

Empty

'-----DCD

L....-

__

Sync

/Hun

t

'-----CTS

L....-

__

Transmi

t Underrun/EOM

L.-.

__

Break/Abort

Rx

Char

Available

(DO).

This

bit

is held

at

logic high,

until

all characters

within

the

receive FIFO stack, are read. Logic

low

indicates

that

no

more

receive characters are available.

Interrupt

Pending (DI).

This

bit

only has significance

in

channel

A.

In

channel

B,

the

bit

is always

at

logic low.

When

set

to

logic high,

the

bit

indicates

that

an

interrupt

condition is

present

within

the

SIO.

Transmit

Buffer

Empty

(D2).

This

bit

is

set

to

logic

high

every

time

a

character

is

transmitted

out

of

the

transmit

Loading...

Loading...