Sweep Start / Stop (to / from A9)

Sweep Start / Stop

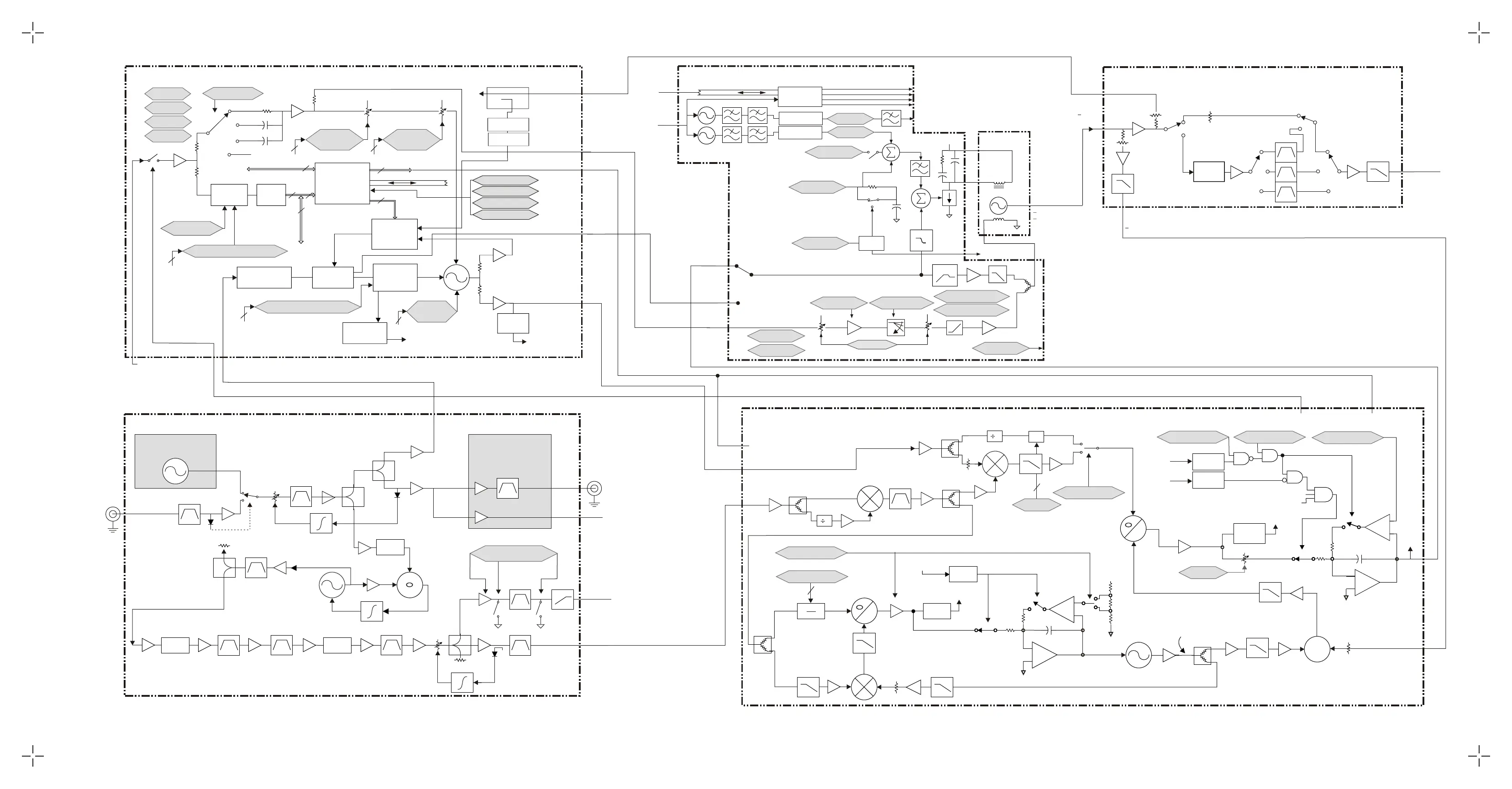

A5 Sampler / YO Loop (Coarse Tune)

1 GHz RF

1 GHz In

250 MHz LO

750 MHz

J1 1 GHz In

Mode B

Mode A

¸P

500 - 1000 MHz +5dBm

Frac-N

In

RF

14 dB

LO

4

IF

f

80 MHz

FM_MODE_A_B

FNDIV

YOLGAIN

STROBE

FM MODE

& MULTR

STROBE

H_PRESET_EN

L_YOPLL_OPEN

YO_PREDAC

1 - Shot

0.2 ms

1 - Shot

1.0 ms

L_YOPLL_PRESET

A Bus

L_HOLD

(from YO Driver) LYOSLEW

(from FRAC-N) LFNSWP

L_YOL_UNLK

YO PLL

Unlock

Detector

YOLGAIN

Sampler IF

30 to 64 MHz

+

_

+

_

MULTR

6

HIGH_LOW

+

_

750 MHz C

750 MHz B

750 MHz 900 MHz

M

x ----

256

Unlock

Detector

155 MHz

Mixer IF

12 to 155 MHz

LO

RF

H_PRESET_EN

+/- 1

L CRS PLL

UNLK

MULTR LATCH

STROBE

L_CRSPLL_Pretune

Vtune

+

_

+15V

VCO

LO

RF

f

S

618 to 905 MHz

f

S

f

YO

YO

Phase-

lock

1- Shot

S

900 MHz

SOURCE_SETTLED_H

LFNSWP

FM_OFF_H

Block Diagram for the PSG Signal Generator Reference / Synthesis Loop, Service Guide E8251-90259

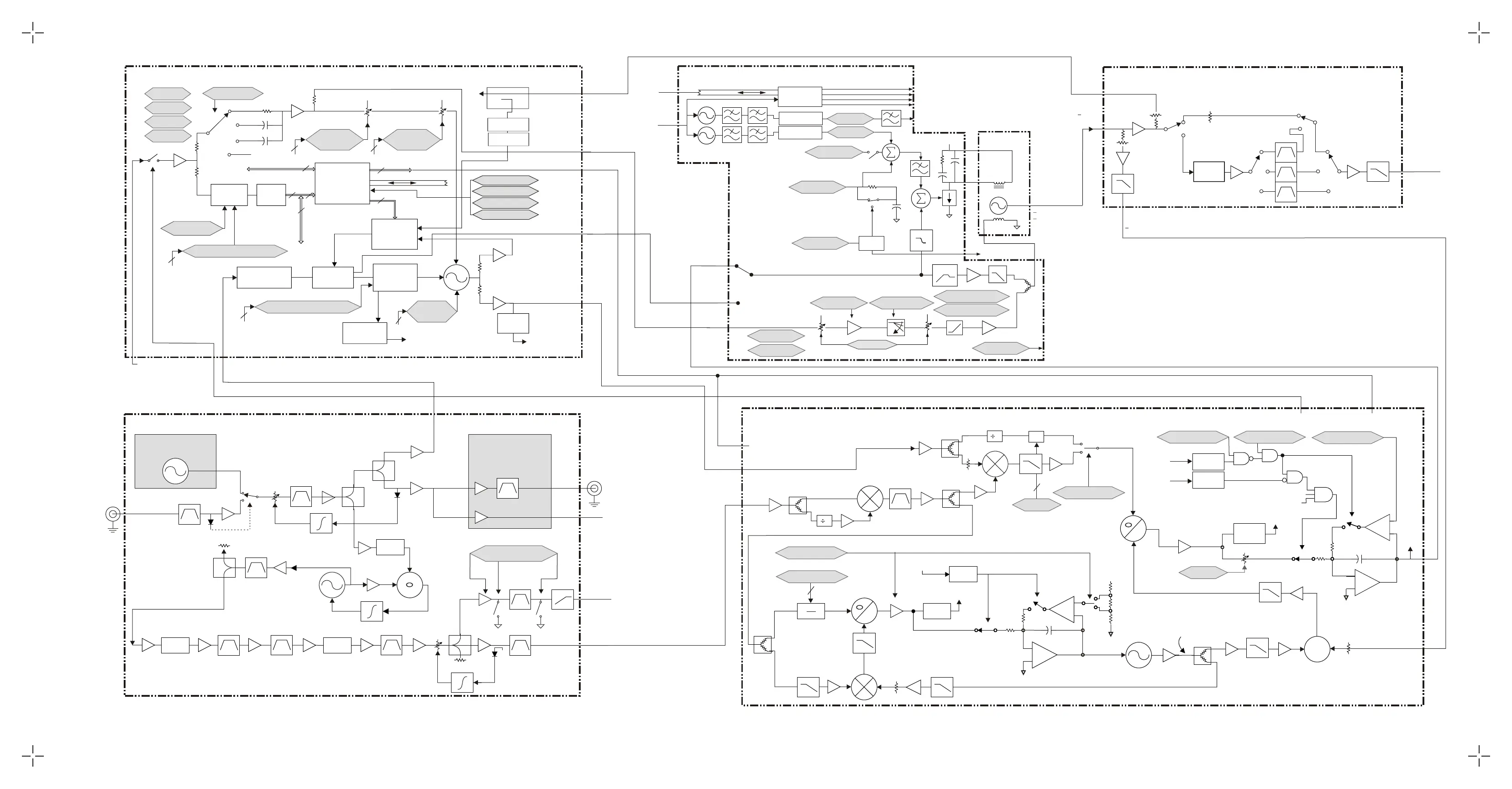

A32 10 MHz

Crystal Oscillator

100 MHz

10 MHz

10 MHz

10 MHz

50 MHz

500 MHz

500 MHz

1 GHz

1 GHz

1 GHz

x 2

x 5

x 10

1 GHz-OUT_LOWBAND

ON / OFF

10 MHz to

A6 Frac-N

100 MHz

1 GHz

Output to

A5 Sampler

1 GHz

Output to

A8 Output

10 MHz

Digital Out to

A11 Pulse / Analog

Modulation Generator

10 MHz Digital Out

Ext

10 MHz

Out

Note: This drawing shows the A7 Reference (Option UNR).

Both the A7 Reference (Standard) and the A7 Reference (Option UNR)

have the same input and output signals.

Ext

10 MHz

In

A7 Reference (Option UNR)

A31 Motherboard

p-ref_synth-loop

X2

Doubler

3-10

10-20

5-10

3-20

Limiter

3-10

3-10

3-10

A29 20 GHz Doubler

750 MHz

16-20

13-16

10-13

80 MHz

to A5 Sampler

3.2 - 10 GHz

> -7 dBm

to A6 Frac-N

3.2 - 10 GHz

> -7 dBm

>3.2 - 20 GHz

H_Speedup Enable

V_GHZ_DAC

A9 YIG Driver

Sweep Out

Rear Panel

(0-10v)

FM

Coil

FM_ATTEN_L

FM_ATTEN_H

FM_GAIN_DAC

FM_FREQ_COMP

FM_FREQ_COMP_L

FM_ATTEN

FM_FREQ_COMP_H

800k

230: :1k

: :

:

:4k

+32 V

Main

Coil

LYO Loop Hold 1

2k

230

Pretune

Speedup

Ramp

Sweep

YIG Pre-tune DAC

Sweep Control

Sweep_DAC

Delay_Coupler DAC

Sweep_DAC

Programmerable

Counter

Programmerable

Counter

YIG

> 3.2-10 GHz

> + 11 dBm

Retrace (Rear Pnl)

Z-axis / Blanking (Rear Pnl)

Stop Sweep (Rear Pnl)

Sweep Level (to A10)

(cw)

sweep=

0V

3.2-10V

J4

from A5

J9

from A6

J3

from A6

Ramp Swp

10MHz

Ref

100Hz

(cw)

J4

J3

J2

500-1000 MHz

Reference Input

10 MHz TCXO

10 dB

to

Analog Bus

VCO Out

VCO

FM

Atten &

Offset

Loop Filter &

Lead-Lag

Reference

Divider /2

5

Control

RF

Power

Detector

Phase

Detector

2

12 dB

5 MHz

FM

Data I/O

VCO

Tune

Reclocked

VCO/N

7

7

7

YTO_FM

H_FM_INV

H_SD_FM

L_SD_OFF

L_FM_OFF

MOD_CONTROL

1 MHz PM

0.1 MHz PM

Z

o

SD

Mod

Control

5

Frac-N

Prescaler

Control

A6 Frac-N (Fine Tune)

9

Source Settled

Indicators

ATTEN_

CONTROL

FM_OUT_

BAND_

DAC

3

16

16

FM

FM

SOURCE_SETTLED_H

3

EE_POT_

CONTROL

from A11 Pulse / Analog

Modulation Generator

FM_OFF_H

GAIN_CONTROL_DAC

Prescaler

FM_IN_BAND_DAC

FM_IN_BAND_OFFSET_DAC

Out of lock

Detector

L_Out_of_Lock

Lowband

Frec-N

Divide

Sweep_YIG Driver

Fixed

Divider

3.2-10GHz

from

A29 Doubler

J1

Programable

Divider

L_WIDELBW

L_POS_PHASE_INCR

STRB

L_RST

to / from

A6

J6

J1

FM Input

A28 YIG

J1

J1

f

I

f

I

I

2

4

Loading...

Loading...