Debug

ARM DDI 0432C Copyright © 2009 ARM Limited. All rights reserved. 6-9

ID112415 Non-Confidential

6.2 Debug register summary

Table 6-6 shows the debug registers. Each of these registers is 32 bits wide.

Table 6-7 shows the BPU registers. Each of these registers is 32 bits wide.

Table 6-8 shows the DWT registers. Each of these registers is 32 bits wide.

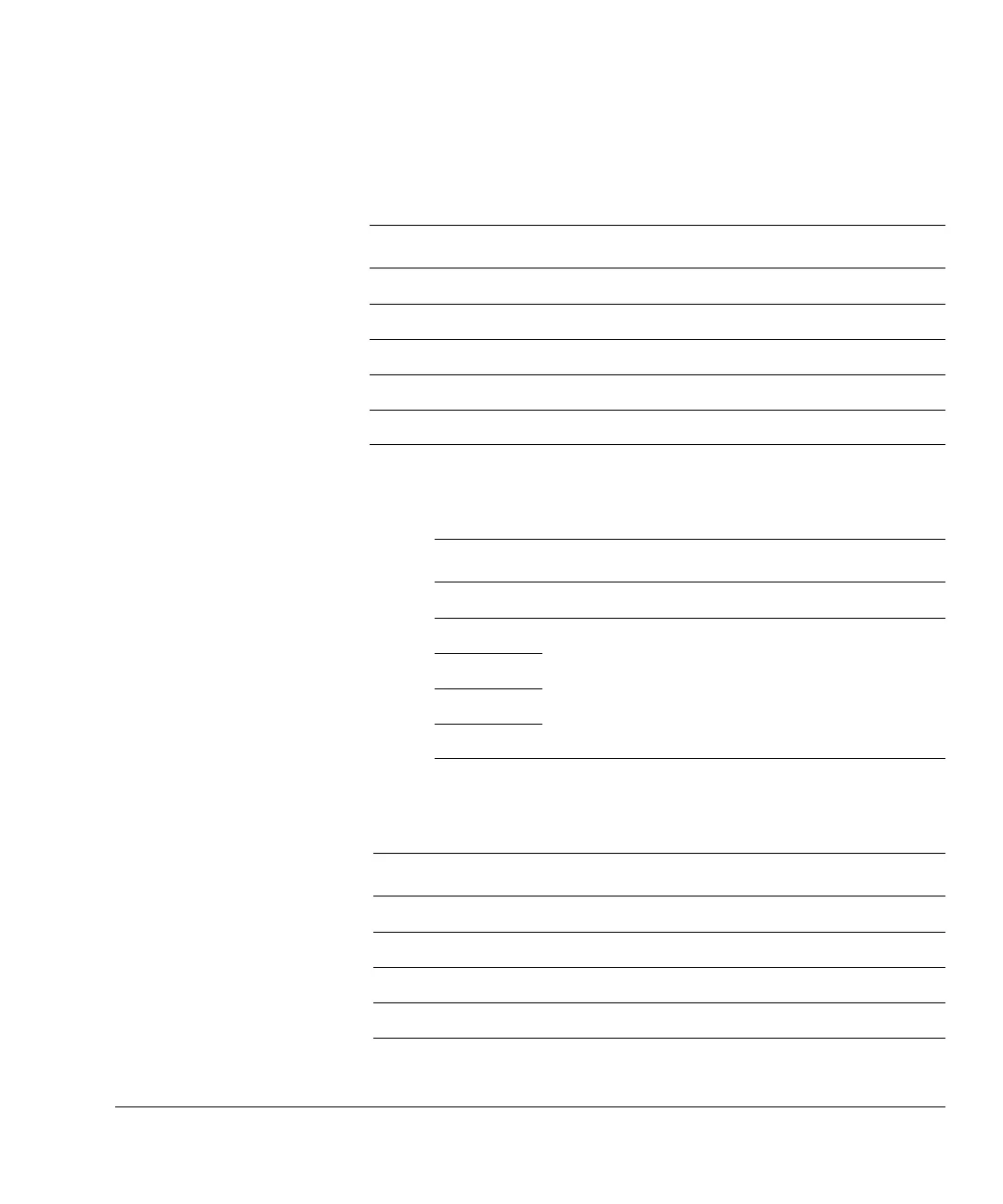

Table 6-6 Debug registers summary

Name Description

DFSR Debug Fault Status Register in the ARMv6-M ARM

DHCSR Debug Halting Control and Status Register in the ARMv6-M ARM

DCRSR Debug Core Register Selector Register in the ARMv6-M ARM

DCRDR Debug Core Register Data Register in the ARMv6-M ARM

DEMCR Debug Exception and Monitor Control Register in the ARMv6-M ARM

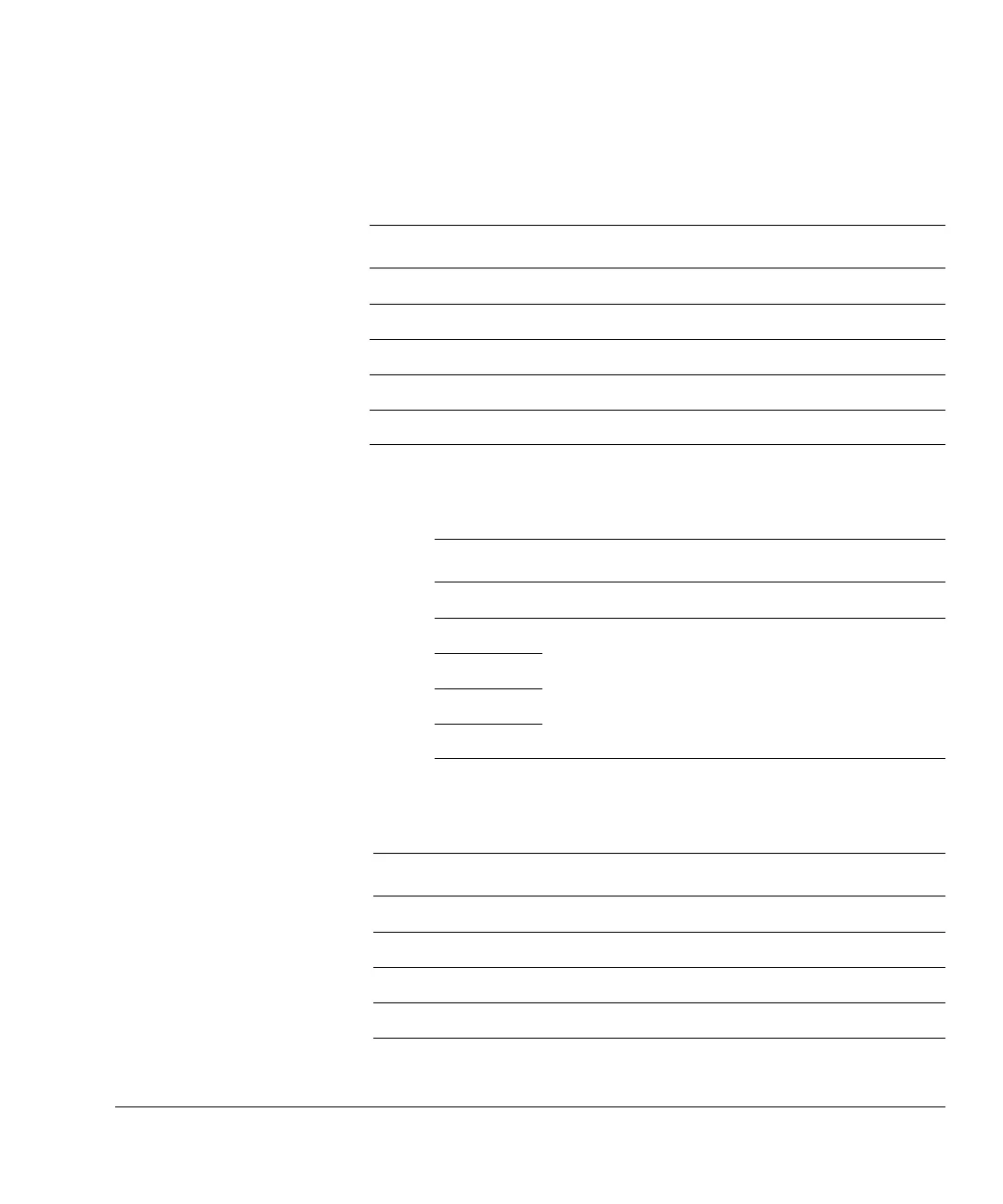

Table 6-7 BPU register summary

Name Description

BP_CTRL Breakpoint Control Register in the ARMv6-M ARM

BP_COMP0 Breakpoint Comparator Registers in the ARMv6-M ARM

BP_COMP1

BP_COMP2

BP_COMP3

Table 6-8 DWT register summary

Name Description

DWT_CTRL Control Register in the ARMv6-M ARM

DWT_PCSR Program Counter Sample Register in the ARMv6-M ARM

DWT_COMP0 Comparator Register in the ARMv6-M ARM

DWT_MASK0 Mask Register in the ARMv6-M ARM

DWT_FUNCTION0 Function Register in the ARMv6-M ARM

Loading...

Loading...