System Control

4-4 Copyright © 2009 ARM Limited. All rights reserved. ARM DDI 0432C

Non-Confidential ID112415

4.2.1 CPUID Register

The CPUID characteristics are:

Purpose Contains the part number, version, and implementation

information that is specific to this processor.

Usage constraints There are no usage constraints.

Attributes See the System control registers on page 4-3.

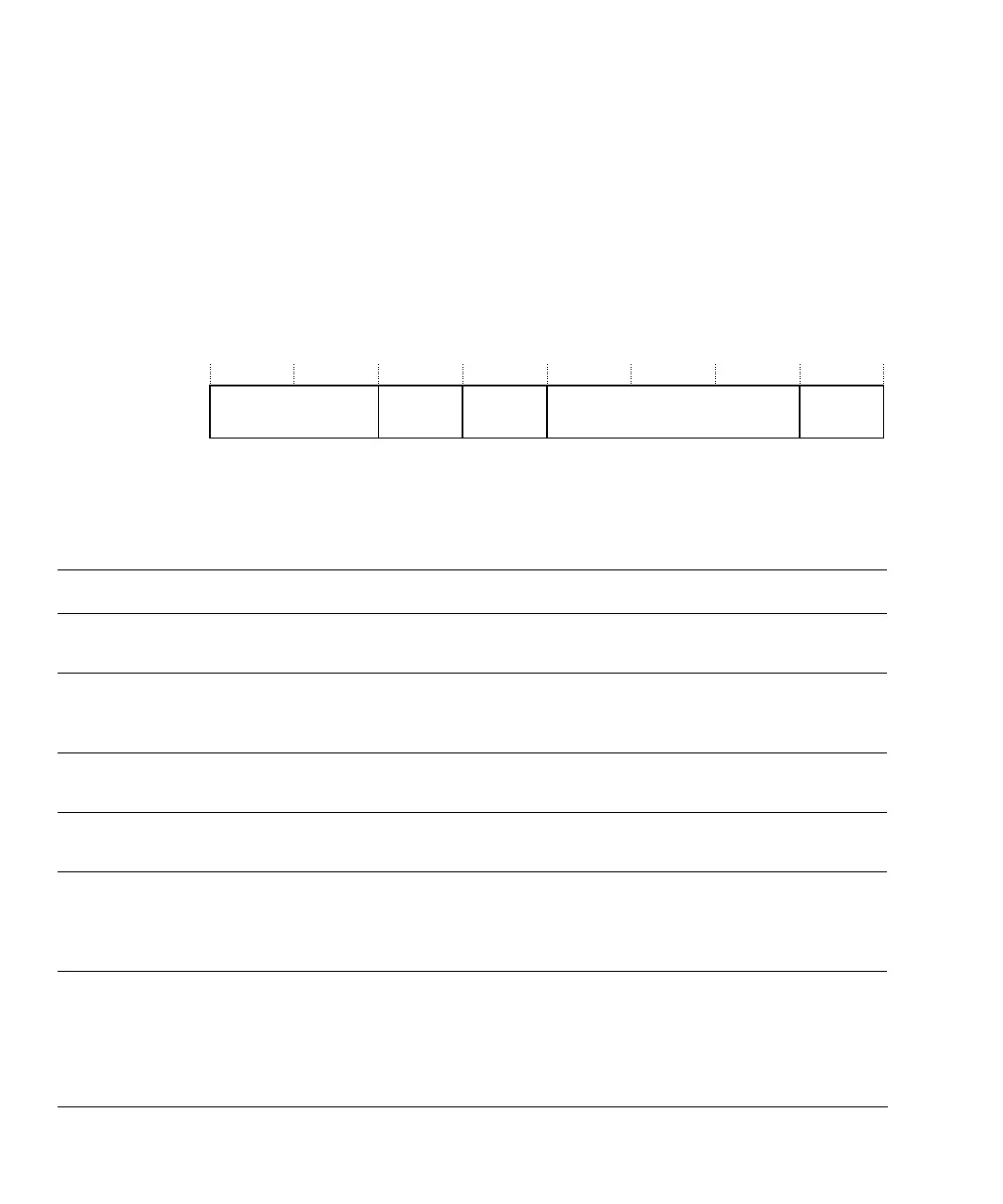

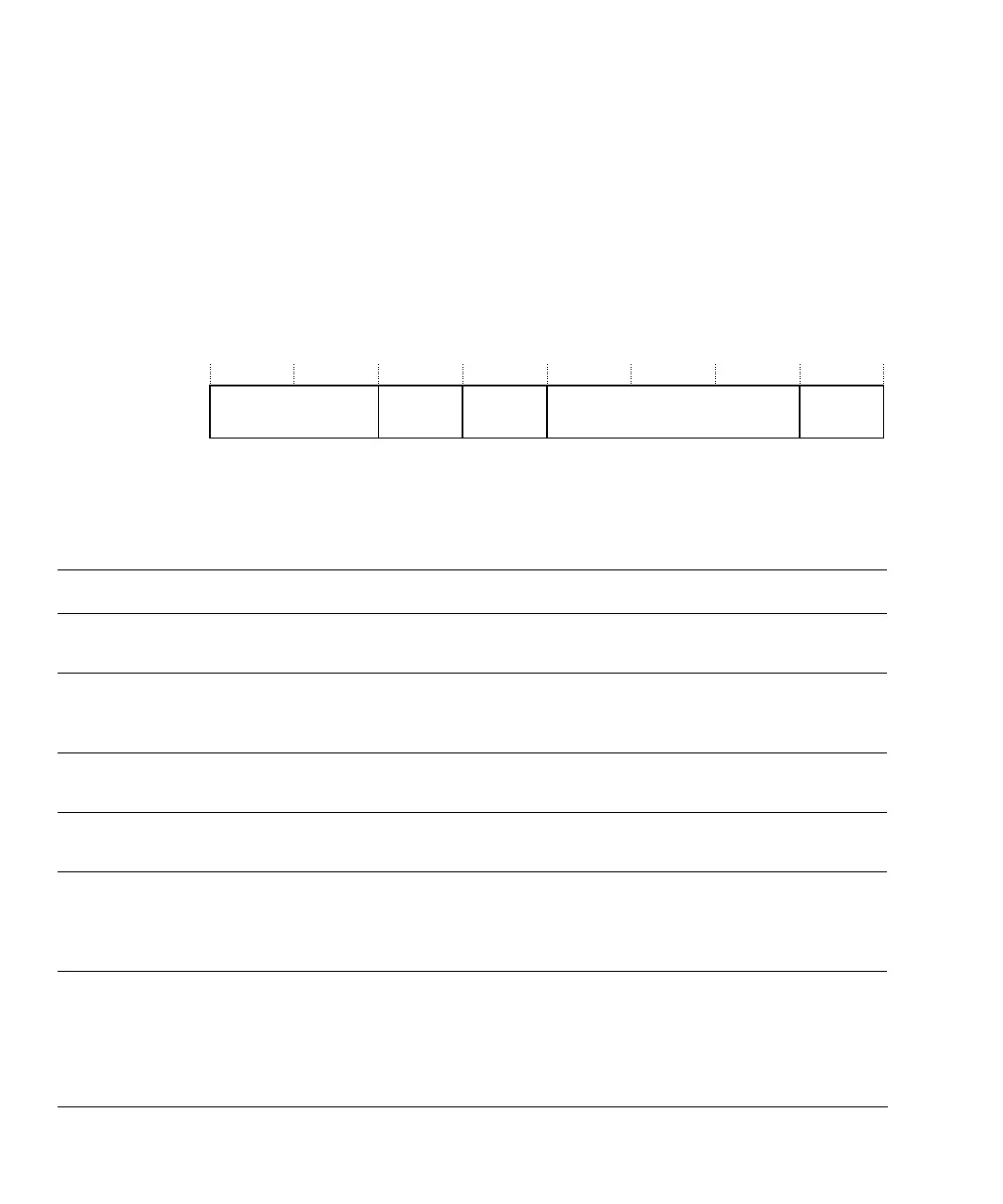

Figure 4-1 shows the CPUID bit register assignments.

Figure 4-1 CPUID bit register assignments

Table 4-2 shows the CPUID register bit assignments.

31 16 15 4 3 0

Implementer

RevisionPartno

24 23 20 19

Variant Constant

Table 4-2 CPUID bit register assignments

Bits Field Function

[31:24] Implementer Implementer code:

0x41

= ARM.

[23:20] Variant Implementation defined. In ARM implementations this is the major revision number n in the

rn part of the rnpn revision status, Product revision status on page xii:

0x0

.

[19:16] Constant Indicates the architecture, ARMv6-M:

0xC

.

[15:4] Partno Indicates part number, Cortex-M0:

0xC20

.

[3:0] Revision Indicates revision. In ARM implementations this is the minor revision number n in the pn part

of the rnpn revision status, see Product revision status on page xii. For example, for release

r0p0:

0x0

.

Loading...

Loading...